# CONDITIONAL TECHNIQUES FOR STREAM PROCESSING KERNELS

# A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Ujval J. Kapasi March 2004

© Copyright by Ujval J. Kapasi 2004 All Rights Reserved I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

William J. Dally (Principal Adviser)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Mark Horowitz

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Christoforos Kozyrakis

Approved for the University Committee on Graduate Studies.

## **Abstract**

The stream programming model casts applications as a set of sequential data streams that are operated on by data-parallel computation kernels. Previous work has shown that this model is a powerful representation for media processing applications, such as image- and signal-processing, because it captures the locality and concurrency inherent to an application. This careful handling of important application properties results in kernels that are compute-intensive—i.e., kernels that perform a large number of arithmetic operations per unit of inter-kernel communication bandwidth. Furthermore, the stream model can be implemented with efficient VLSI designs, such as the Imagine Programmable Stream Processor. The Imagine chip supports 48 ALUs on a single die, operating at over 200MHz. This large number of ALUs provides a high peak performance, but makes efficiently executing kernels with conditional code a challenge.

We will introduce two techniques for efficiently supporting kernel conditionals, such as if-statements, case-statements, and while-loops: conditional routing and conditional streams. Conditional routing is a code transformation that exploits the trade-off of increasing inter-kernel communication in order to increase the performance of kernel inner-loops containing conditional code. The second technique we will discuss is the use of a conditional stream, which is a mechanism to reduce the amount of load-imbalance that arises between parallel processing clusters on a single stream processor chip. Load-imbalance results when different conditional paths are taken on different processing clusters, and causes one or more of the clusters to wait idle for the others to complete a kernel. We will also present a case study of the impact of these techniques on a programmable polygon rendering pipeline that contains many unpredictable conditionals. We show that our techniques improve the performance of this application by 1.9×.

# Acknowledgments

Dedicated to the late Chandulal K. Kapasi

I am truly fortunate to have had the opportunity to work with my adviser, Bill Dally, these past few years. He has, by example, taught me to set the bar as high as possible, and then a little higher yet. I am overwhelmed by gratitude for his patience and guidance throughout my graduate student career. I look forward to working with Bill outside of Stanford as we embark on a new venture to commercialize our Stanford research. I am also indebted to Mark Horowitz and Christos Kozyrakis for many educational interactions, and for significantly helping to improve the work in this dissertation.

Another critical support group during my Stanford tenure has been the Imagine project team members. A group experience as positive and successful as ours is rare. I would particularly like to thank the original Stanford members: Scott Rixner, Brucek Khailany, John Owens, and Peter Mattson. More recently Brian Towles, Jinyung Namkoong, Ben Serebrin, Jung Ho Ahn, and Abhishek Das have been important collaborators in ensuring the longevity of our research. Many of the ideas in this dissertation have been molded during white-board discussions with these people.

My officemates over the years have provided valuable relief and encouragement when I needed it. Brian Towles, Sarah Harris, and Steve Lacy have been wonderful officemates, and I will miss them after I leave Stanford. I would also like to thank the CVA group administrators, Pamela Elliot and Shelley Russell. They ensured that I could focus on my research by handling all of the administrative details. Similarly, the National Science Foundation Fellowship and the Stanford Graduate Fellowship enabled me to pursue my research without financial concerns.

Finally, I am eternally thankful to my family. Mom, Dad, Anokhi: you guys believed

in me, and it is largely because of your constant support and encouragement that I am completing my Ph.D. To my new wife, Kristin: you have provided me with inspiration in all walks of life, and I leave Stanford excited to begin the rest of my life with you.

# **Contents**

| Al | Abstract        |         |                                                 |    |

|----|-----------------|---------|-------------------------------------------------|----|

| A  | Acknowledgments |         |                                                 | v  |

| 1  | Intr            | oductio | n                                               | 1  |

|    | 1.1             | Condi   | tionals are Challenging                         | 2  |

|    | 1.2             | Resear  | rch Contributions                               | 2  |

|    | 1.3             | Thesis  | Roadmap                                         | 3  |

| 2  | Stre            | am Pro  | ocessing                                        | 5  |

|    | 2.1             | Strean  | n Programming Model                             | 7  |

|    |                 | 2.1.1   | Example Application                             | 7  |

|    |                 | 2.1.2   | Locality and Concurrency                        | 10 |

|    |                 | 2.1.3   | High-Level Stream Languages                     | 11 |

|    | 2.2             | Progra  | ammable Stream Processors                       | 12 |

|    |                 | 2.2.1   | Instruction Set Architecture (ISA)              | 13 |

|    |                 | 2.2.2   | Micro-Architecture                              | 16 |

|    | 2.3             | Kerne   | l Conditionals                                  | 20 |

|    |                 | 2.3.1   | Motivating Example: The <i>geom_rast</i> Kernel | 21 |

|    |                 | 2.3.2   | Challenges                                      | 23 |

| 3  | VLI             | W Sche  | eduling with Conditional Routing                | 25 |

|    | 3.1             | Motiva  | ation                                           | 25 |

|    |                 | 3.1.1   | Existing Techniques: If-statements              | 26 |

|   |     | 3.1.2   | Existing Techniques: While-loops              | 30       |

|---|-----|---------|-----------------------------------------------|----------|

|   | 3.2 | Apply   | ing Conditional Routing to If-Statements      | 31       |

|   |     | 3.2.1   | Performance                                   | 36       |

|   |     | 3.2.2   | Comparison to Other Techniques                | 41       |

|   |     | 3.2.3   | Technique Selection                           | 49       |

|   |     | 3.2.4   | SRF Allocation                                | 58       |

|   |     | 3.2.5   | Conditional Routing Summary for If-Statements | 59       |

|   | 3.3 | Apply   | ing Conditional Routing to While-Loops        | 61       |

|   |     | 3.3.1   | Expanded Conditional Routing                  | 62       |

|   |     | 3.3.2   | Flattened Conditional Routing                 | 65       |

|   |     | 3.3.3   | State-Unrolling                               | 68       |

|   |     | 3.3.4   | Performance                                   | 71       |

|   |     | 3.3.5   | Ordering                                      | 77       |

|   |     | 3.3.6   | Conditional Routing Summary for While-Loops   | 83       |

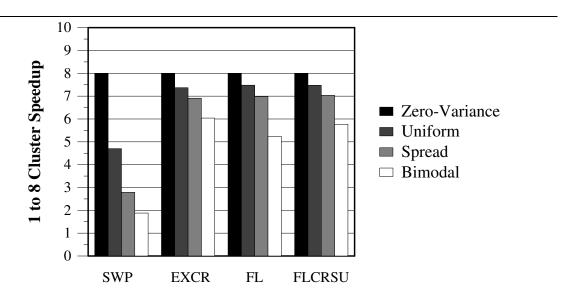

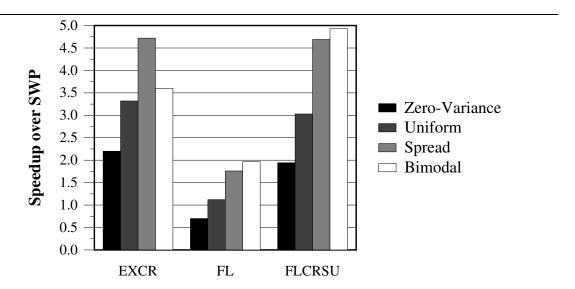

|   | 3.4 | REND    | DER Performance                               | 86       |

|   | 3.5 | Dynan   | nic Techniques                                | 90       |

| 4 | SIM | D Perfo | ormance with Conditional Routing              | 91       |

|   | 4.1 |         | ation                                         | 92       |

|   | 4.2 |         | mance                                         |          |

|   |     | 4.2.1   |                                               | 94       |

|   |     | 4.2.2   |                                               | 97       |

|   | 4.3 | REND    | DER Performance                               | 98       |

|   |     | 4.3.1   | MIMD Comparison                               |          |

|   | 4.4 | Summ    | ary                                           |          |

| _ |     |         |                                               |          |

| 5 |     |         | 8                                             | 02       |

|   | 5.1 |         | ation                                         |          |

|   | 5.2 |         | ng Techniques for Improving Load-Balance      |          |

|   | 5.3 |         | tional Streams                                |          |

|   |     | 5.3.1   | If-Statements                                 |          |

|   |     | 522     | While I cons                                  | $\Omega$ |

|     | 5.4 Implementation |          |                                          | . 109 |

|-----|--------------------|----------|------------------------------------------|-------|

|     |                    | 5.4.1    | Hardware Overview                        | . 110 |

|     |                    | 5.4.2    | Hardware Details                         | . 112 |

|     |                    | 5.4.3    | Scalability                              | . 119 |

|     | 5.5                | Perfor   | mance                                    | . 126 |

|     |                    | 5.5.1    | If-statements                            | . 127 |

|     |                    | 5.5.2    | While-loops                              | . 129 |

|     |                    | 5.5.3    | Impact of SRF Communication              | . 130 |

|     | 5.6                | Other    | Uses of Conditional Streams              | . 132 |

|     | 5.7                | REND     | DER Performance                          | . 133 |

|     | 5.8                | Summ     | ary                                      | . 136 |

| 6   | Con                | clusions | s                                        | 137   |

|     | 6.1                | Condit   | tional Routing                           | . 138 |

|     | 6.2                | Condit   | tional Streams                           | . 139 |

|     | 6.3                | A Con    | npiler Framework                         | . 140 |

| 4   | The                | IMAGI    | NE Stream Processor                      | 142   |

|     | A.1                | Condit   | tional Streams Implementation on Imagine | . 144 |

| Ril | hliogi             | anhv     |                                          | 148   |

# **List of Tables**

| 3.1                               | Summary of if-statement conditional techniques 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2                               | Summary of while-loop conditional techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.3                               | Impact of conditional routing on VLIW schedule of geom_rast 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.1                               | 1 to 8 cluster speedup of existing techniques on <i>geom_rast</i> 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.2                               | 8-cluster performance of existing techniques on <i>geom_rast.</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.3                               | Impact of conditional routing on eight-cluster performance of RENDER 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.1                               | Instructions supported by the conditional stream unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.2                               | Instruction sequences for executing conditional stream accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                   | more and the most |

| 5.3                               | Stream buffer specific state stored in the conditional stream unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <ul><li>5.3</li><li>5.4</li></ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                   | Stream buffer specific state stored in the conditional stream unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.4                               | Stream buffer specific state stored in the conditional stream unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# **List of Figures**

| 2.1  | Streams and a kernel from an MPEG-2 video encoder application                | 8  |

|------|------------------------------------------------------------------------------|----|

| 2.2  | MPEG-2 I-frame encoder mapped to streams and kernels                         | 10 |

| 2.3  | A programmable stream processor                                              | 13 |

| 2.4  | Kernel execution unit (KEU) architecture                                     | 16 |

| 2.5  | KEU organizations for multi-cluster execution models                         | 18 |

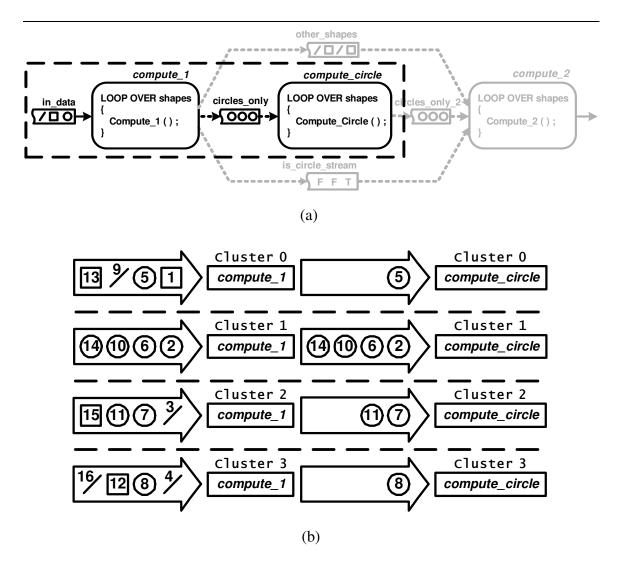

| 3.1  | Applying conditional routing to a kernel containing an if-statement          | 33 |

| 3.2  | Impact of conditional routing for if-statements on application-level code    | 34 |

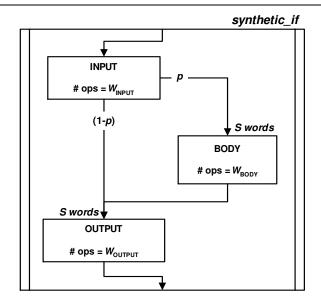

| 3.3  | The synthetic_if benchmark                                                   | 39 |

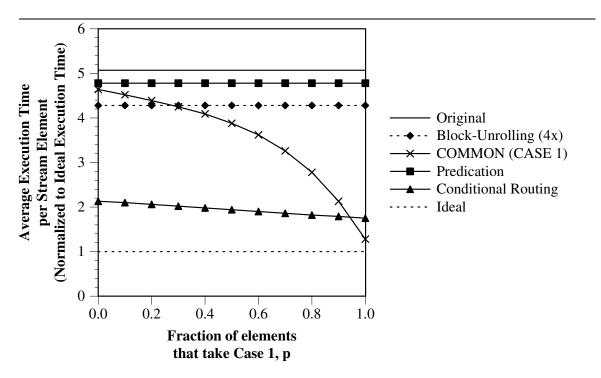

| 3.4  | Impact of conditional routing on execution time for synthetic_if             | 41 |

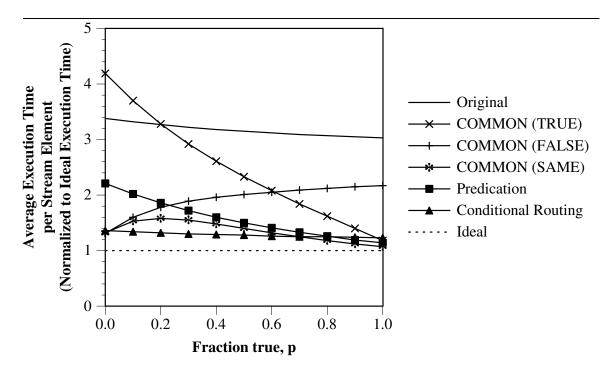

| 3.5  | Comparison of conditional routing and existing techniques for if-statements. | 42 |

| 3.6  | Results of conditional techniques on synthetic_if_else                       | 47 |

| 3.7  | Results of conditional techniques on synthetic_case                          | 48 |

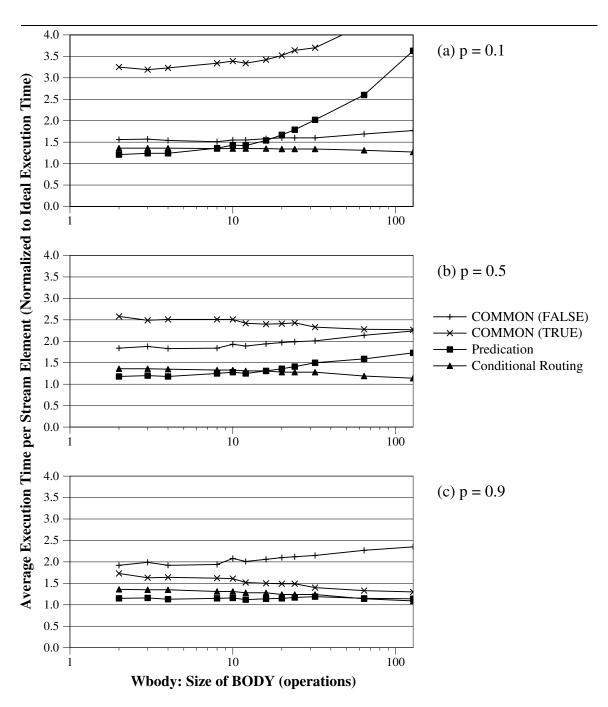

| 3.8  | Impact of number of operations in ${\tt BODY}$ on if-statement techniques    | 51 |

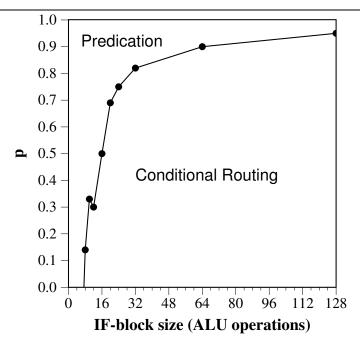

| 3.9  | Technique selection function for the <i>synthetic_if</i> kernel              | 52 |

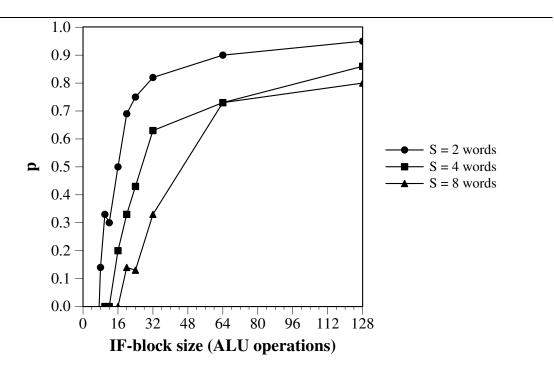

| 3.10 | Impact of SRF communication on CONDITIONAL ROUTING and PREDI-                |    |

|      | CATION                                                                       | 54 |

| 3.11 | Impact of SRF communication on if-statement techniques                       | 55 |

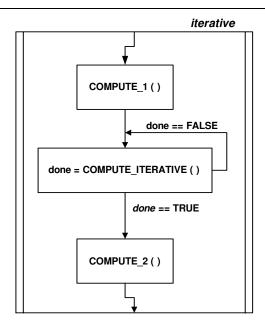

| 3.12 | iterative, an example kernel with a while-loop                               | 62 |

| 3.13 | Expanding a while-loop                                                       | 63 |

| 3.14 | Application-level pseudo-code for expanded conditional routing               | 64 |

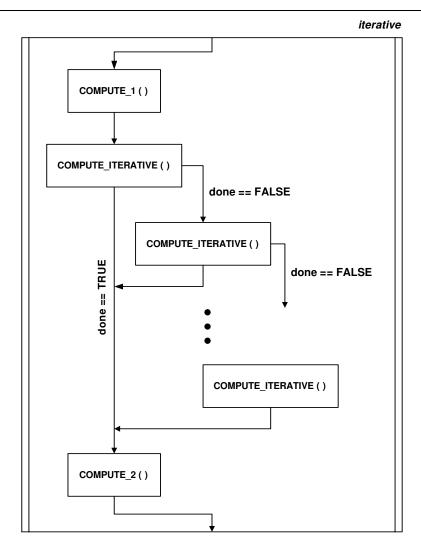

| 3.15 | Loop-flattening the <i>compute_iterative</i> kernel                          | 67 |

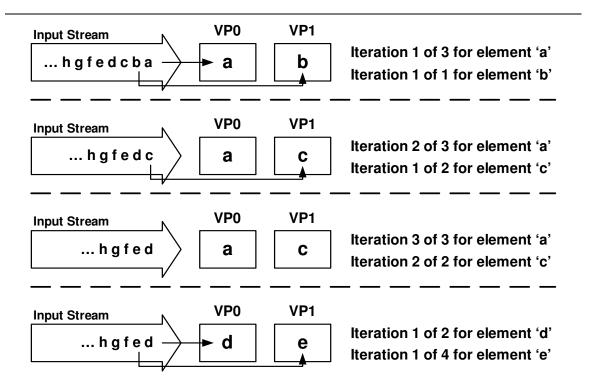

| 3.16 | Virtual processor view of state-unrolling                                    | 69 |

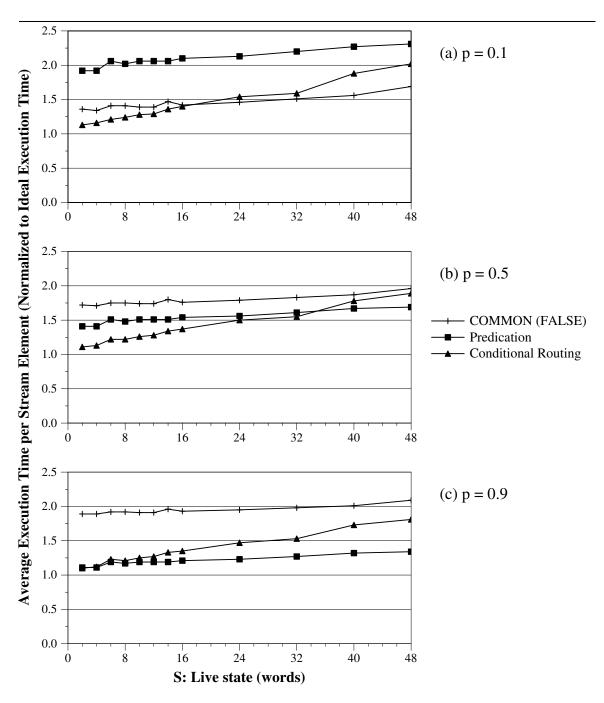

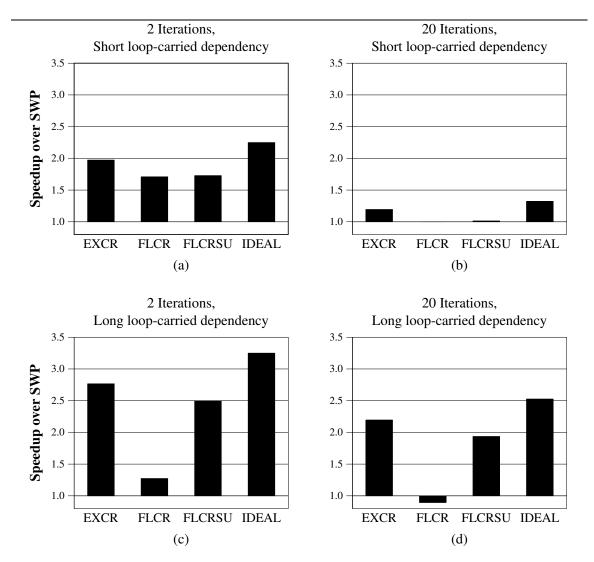

| 3.17 | Impact of conditional routing on synthetic_while                             | 73 |

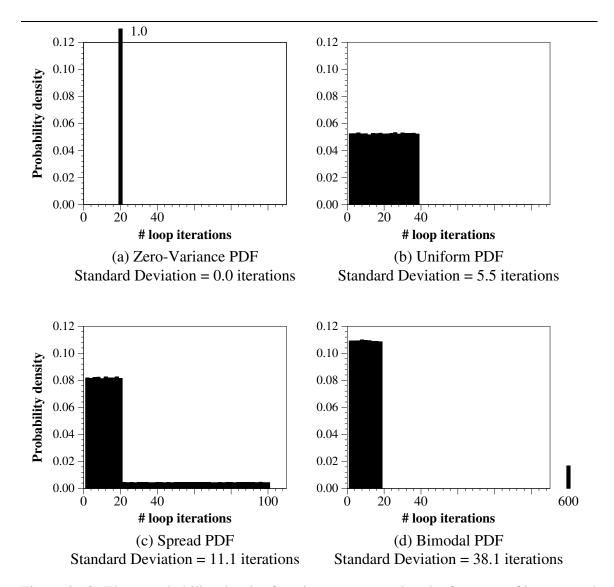

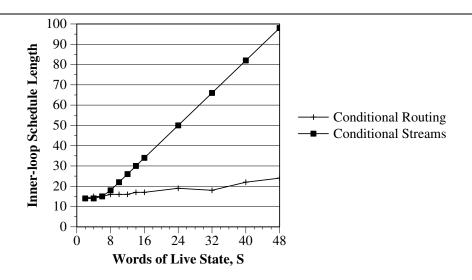

| 3.18 | PDFs used to study impact of correlation on while-loop performance 7                 | 75 |

|------|--------------------------------------------------------------------------------------|----|

| 3.19 | Impact of the distribution of iterations in the input set on synthetic_while 7       | 76 |

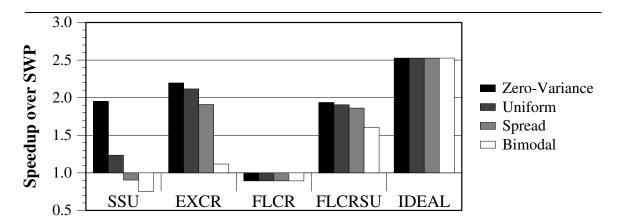

| 3.20 | Impact of sorting the output of <i>synthetic_while</i> to retain original ordering 8 | 30 |

| 3.21 | Performance of alternate methods for sorting the output of synthetic_while 8         | 32 |

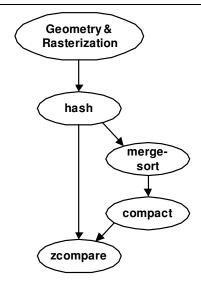

| 3.22 | Polygon rendering application stream and kernel diagram                              | 37 |

| 3.23 | Basic block diagram for the <i>geom_rast</i> kernel                                  | 38 |

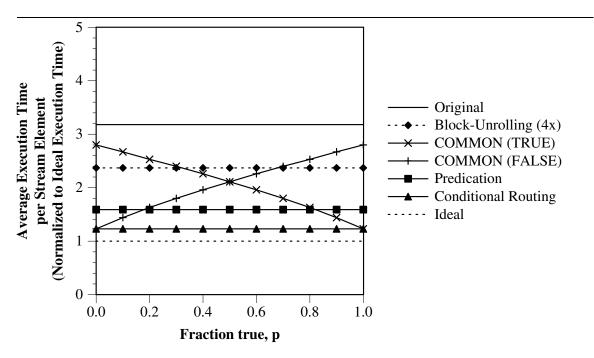

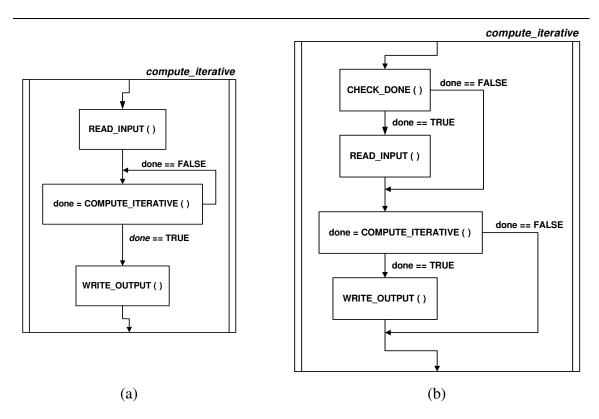

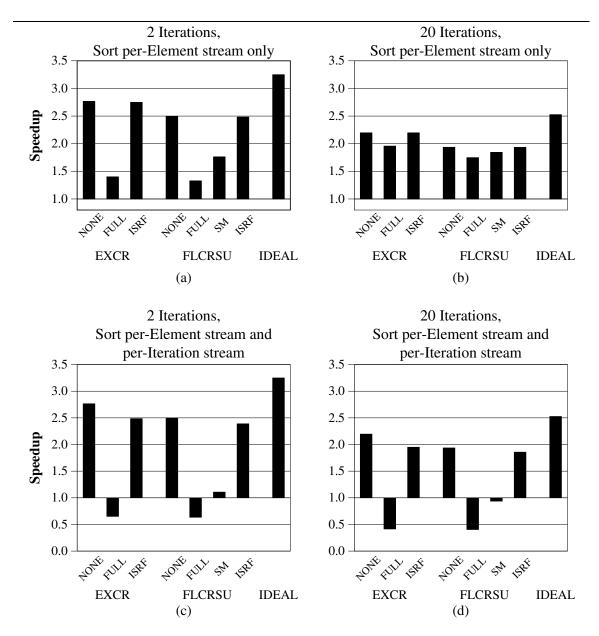

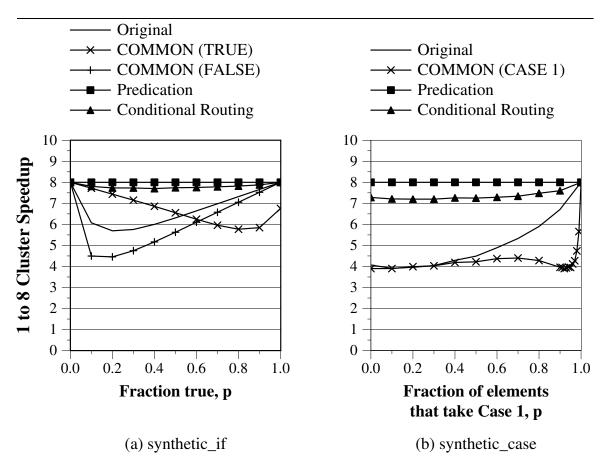

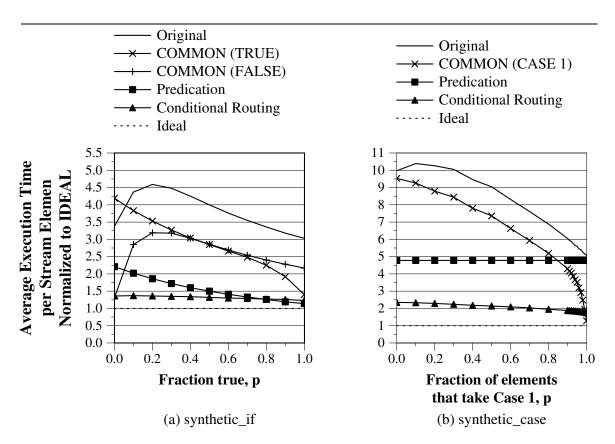

| 4.1  | Impact of SIMD execution model on if-statement techniques                            | 95 |

| 4.2  | Comparison of if-statement techniques on an eight-cluster SIMD machine 9             | 96 |

| 4.3  | Impact of SIMD execution model on while-loop techniques                              | 97 |

| 4.4  | Comparison of while-loop techniques on an eight-cluster SIMD machine 9               | 99 |

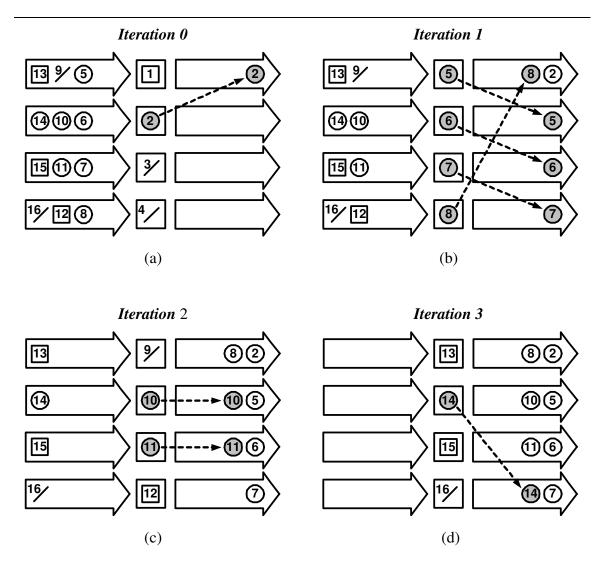

| 5.1  | Load-imbalance due to conditional routing on a SIMD architecture 10                  | )6 |

| 5.2  | Eliminating load-imbalance using a conditional output stream                         | )7 |

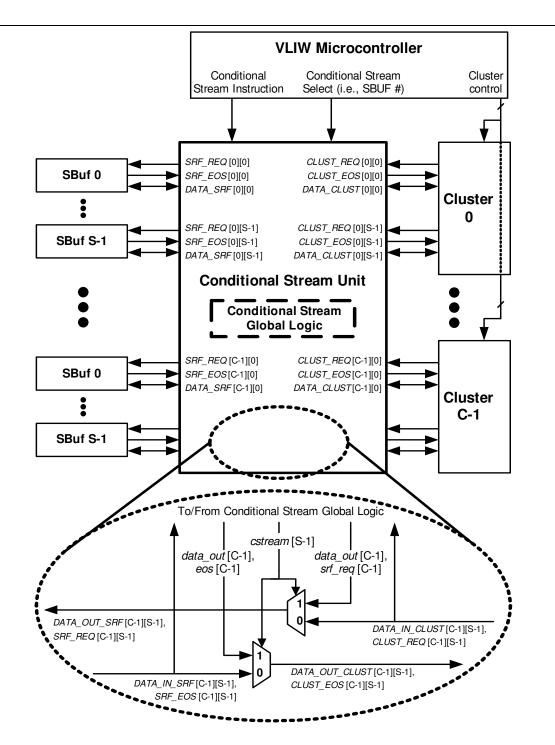

| 5.3  | Conditional stream implementation overview for a SIMD architecture 11                | 1  |

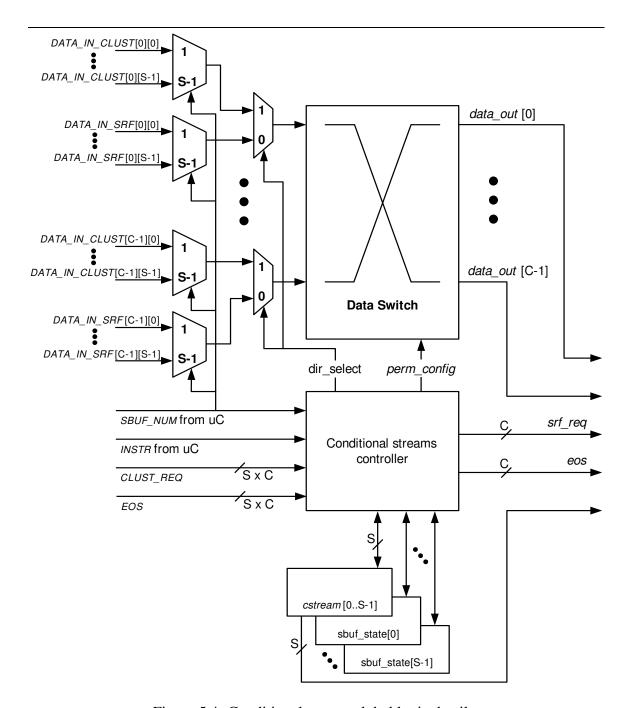

| 5.4  | Conditional stream global logic details                                              | 13 |

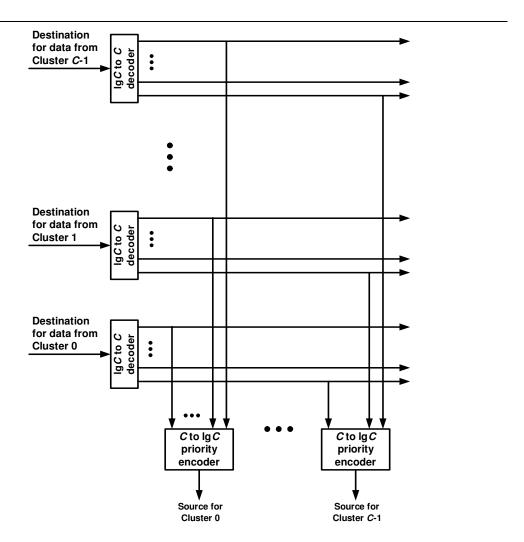

| 5.5  | Naïve GEN_CO_STATE implementation                                                    | 22 |

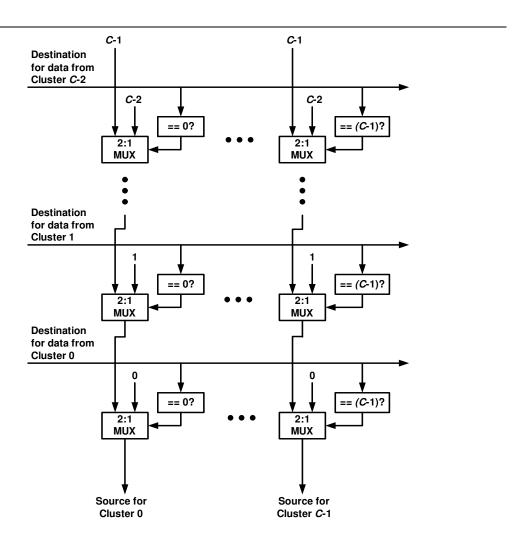

| 5.6  | Improved GEN_CO_STATE implementation for large numbers of clusters 12                | 24 |

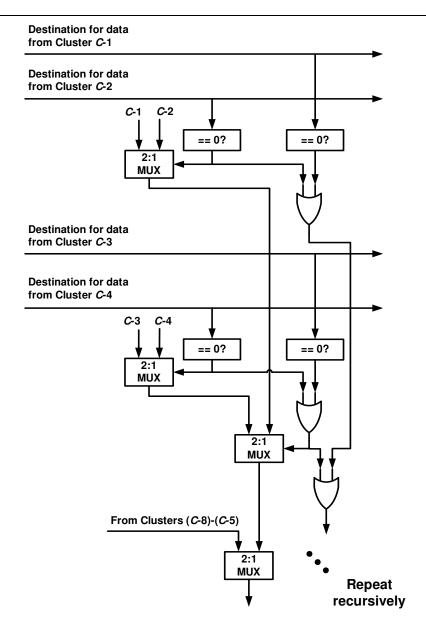

| 5.7  | Log-time hardware search implementation for GEN_CO_STATE                             | 25 |

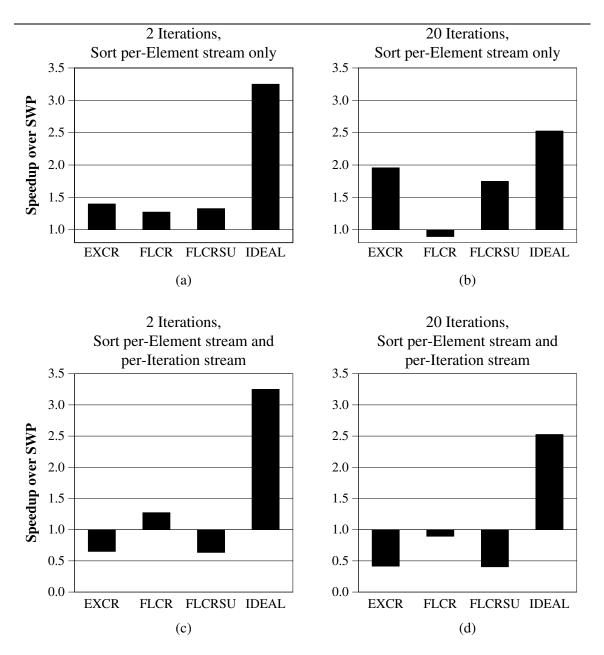

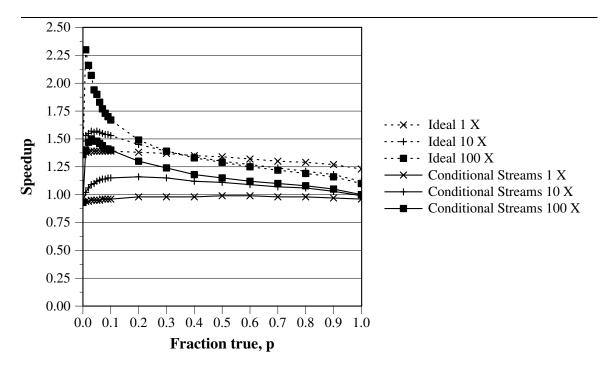

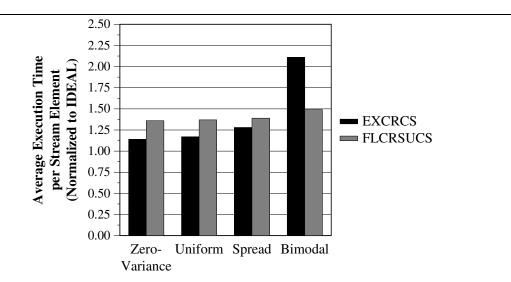

| 5.8  | Conditional stream speedup for if-statements                                         | 28 |

| 5.9  | Conditional stream results for <i>synthetic_while</i>                                | 31 |

| 5.10 | Impact of SRF communication on conditional stream version of <i>input</i> 13         | 31 |

| A.1  | The Imagine Processor architecture block diagram and floor-plan 14                   | 13 |

| A.2  | Use of a buffer for conditional streams with Imagine-style SRF                       | 16 |

# **List of Kernels**

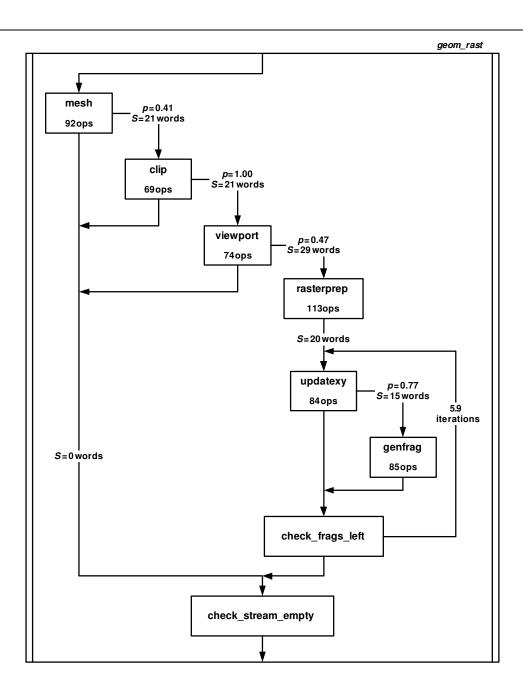

| 2.1 | geom_rast                                                                        | 22 |

|-----|----------------------------------------------------------------------------------|----|

| 3.1 | compute_1                                                                        | 35 |

| 3.2 | compute_2                                                                        | 36 |

| 3.3 | synthetic_if                                                                     | 40 |

| 3.4 | synthetic_if optimized using speculation                                         | 44 |

| 3.5 | synthetic_if optimized using predication                                         | 46 |

| 3.6 | compute_iterative after applying loop-flattening                                 | 68 |

| 3.7 | compute_iterative after applying loop-flattening and state-unrolling             | 70 |

| 3.8 | synthetic_while                                                                  | 71 |

| 5.1 | compute_iterative with loop-flattening, updated for conditional input streams. 1 | 19 |

# Chapter 1

# Introduction

Recent research has shown that programmable stream processors efficiently support large numbers of ALUs on a single chip to achieve a high sustained performance on media processing applications, such as 2-D and 3-D graphics, image processing, and signal processing [Kapasi *et al.*, 2003; Khailany *et al.*, 2001]. Furthermore, stream processors dissipate considerably less power per operation than traditional programmable processors. For example, the *IMAGINE* streaming media processor supports 48 ALUs on a single die in a  $0.15\mu m$  process. At the most power-efficient operating voltage of 1.2V, the processor sustains between 1.4 and 2.2 GFLOPS at 1.9W on representative media processing applications.

It turns out that many media processing applications are very regular: they repetitively perform the same set of operations on a large set of similar data elements. This can be modeled as a sequence of computation *kernels* that operate on data *streams*, where each kernel applies the same function to all the records in a stream. As we will see in the next chapter, stream processors are optimized to exploit this regularity, and this is in part why they are so efficient from a hardware perspective.

### 1.1 Conditionals are Challenging

However, the flip-side is that it is a challenge to efficiently execute conditionals, such as if-then-else statements and while-loops, since they seem to break this regularity assumption (Section 2.3 will discuss this in more detail). The end result is that the presence of data-dependent conditionals in an application reduces the fraction of the peak processor performance achieved. To address this, we will introduce new solutions that increase the performance of applications with data-dependent conditionals on stream processors. For example, the conditional techniques we introduce are able to speed up an OpenGL polygon rendering pipeline 1.9x over an implementation that only uses other existing techniques, such as speculation and predication. Furthermore, on *IMAGINE*, the additional hardware dedicated to our new conditional techniques occupies only about 1% of the chip area.

We are concerned with media processing applications in this thesis, and in particular, we will focus on a 3-D OpenGL polygon rendering pipeline. However, as stream processing technology matures, we envision that the contributions in this thesis will apply to other application domains as well. In fact, the techniques discussed here may become even more important as we try to reap the benefits of efficient stream processing hardware on increasingly difficult (i.e., irregular) applications.

### 1.2 Research Contributions

The primary contributions of this thesis to the fields of computer architecture and stream processing are:

1. A kernel-level code transformation, *conditional routing*, that improves the performance of kernels that contain conditional constructs, such as if- and case-statements and while-loops. Conditional routing improves kernel schedules on VLIW clusters by replacing conditional branches with conditional communication. Removing the conditional branches also enables efficient execution on stream processors that are built using a single-instruction multiple-data (SIMD) array of processing clusters.

- 3

- 2. A kernel-level code transformation, *state unrolling*, that improves the VLIW schedules of while-loops inside kernel main loops. State-unrolling is especially important when there is a long loop-carried dependency in the while-loop, rendering traditional loop-unrolling or software-pipelining ineffective.

- 3. A new mechanism, called *conditional streams*, which improves the load-balance between parallel processing clusters during kernel execution.

- 4. A micro-architecture for accelerating the performance of conditional stream operations.

- An evaluation of the impact of the newly introduced conditional techniques on the performance of a 3-D polygon rendering application, which contains many conditional statements in its kernels.

### 1.3 Thesis Roadmap

In Chapter 2 we will motivate why stream processors are an interesting class of machines for the media processing domain, how they are built, and how they operate. In particular, we will show that stream processors can efficiently support a large number of ALUs by using a SIMD array of processing clusters, where each processing cluster is a statically scheduled VLIW engine. While stream processors are great at executing very regular codes, we will show that efficiently executing code with conditionals is a challenge on these stream processors. We will discuss three specific challenges introduced by the presence of conditionals: improving VLIW schedules, enabling efficient performance on the restrictive SIMD execution model, and reducing the load-imbalance between multiple processing clusters. Each of the next three chapters is devoted to addressing each of these challenges in turn.

Chapter 3 focuses on how one of our new techniques, *conditional routing*, addresses the first challenge. We will show that compared to existing techniques, conditional routing enables efficient VLIW schedules by converting conditional branches to conditional communication. Conditional routing can be applied to both if-statements and while-loops. We

will also introduce another new technique, state unrolling, and show that it should be used in conjunction with conditional routing in order to improve the performance of while-loops even further.

The second challenge is addressed in Chapter 4. In this chapter we show that conditional routing enables efficient performance on stream processors with an array of SIMD processing clusters. The SIMD execution model is attractive because it enables simplified hardware, but in return places restrictions on control-flow. We will show how the performance of kernels implemented using conditional routing, unlike other techniques, is not reduced by these control-flow restrictions.

We address the third and final challenge in Chapter 5. This chapter shows how *conditional streams* reduce the load-imbalance between multiple clusters in a stream processor. Since conditional streams require hardware acceleration for good performance, we will present a micro-architecture to support them in this chapter.

Finally, we will present our conclusions in Chapter 6, and indicate fruitful areas for further research based on these conclusions.

# Chapter 2

# **Stream Processing**

The complexity of modern media processing, including 3D graphics, image compression, and signal processing, requires tens to hundreds of billions of computations per second. To achieve these computation rates, current media processors use special-purpose architectures tailored to one specific application. Such processors require significant design effort and are thus difficult to change as media-processing applications and algorithms evolve.

The demand for flexibility in media processing motivates the use of programmable processors. However, very large-scale integration constraints limit the performance of traditional programmable architectures. In modern VLSI technology, computation is relatively cheap—thousands of arithmetic logic units (ALUs) that operate at multi-gigahertz rates can fit on a modestly sized 1-cm<sup>2</sup> die. The problem is that delivering instructions and data to those ALUs is prohibitively expensive. For example, only 6.5 percent of the Itanium 2 die is devoted to the 12 integer and two floating-point ALUs and their register files [Naffziger *et al.*, 2002]; communication, control, and storage overhead consume the remaining die area. In contrast, the more efficient communication and control structures of a special-purpose graphics chip, such as the Nvidia GeForce4 [Montrym and Moreton, 2002], enable the use of many hundreds of floating-point and integer ALUs to render 3D images.

In part, such special-purpose media processors are successful because media applications have abundant parallelism—enabling thousands of computations to occur in parallel—and require minimal global communication and storage—enabling data to pass directly from one ALU to the next. A stream architecture exploits this locality and concurrency by

partitioning the communication and storage structures to support many ALUs efficiently:

- operands for arithmetic operations reside in local register files (LRFs) near the ALUs, in much the same way that special-purpose architectures store and communicate data locally;

- streams of data capture coarse-grained locality and are stored in a stream register file (SRF), which can efficiently transfer data to and from the LRFs between major computations; and

- global data is stored off-chip only when necessary.

These three explicit levels of storage form a data bandwidth hierarchy with the LRFs providing an order of magnitude more bandwidth than the SRF and the SRF providing an order of magnitude more bandwidth than off-chip storage. This bandwidth hierarchy is well matched to the characteristics of modern VLSI technology, as each level provides successively more storage and less bandwidth. By exploiting the locality inherent in media-processing applications, this hierarchy stores the data at the appropriate level, enabling hundreds of ALUs to operate at close to their peak rate. Moreover, a stream architecture can support such a large number of ALUs in an area- and power-efficient manner. Modern high-performance microprocessors and digital signal processors continue to rely on global storage and communication structures to deliver data to the ALUs; these structures use more area and consume more power per ALU than a stream processor.

An example of a stream processor is the *IMAGINE* Processor (Appendix A), which targets the media processing application domain [Khailany *et al.*, 2001; Rixner *et al.*, 1998]. While retaining complete programmability, *IMAGINE* delivers roughly four times the peak performance of TI's high-performance floating-point DSP, the TMS320C6713 [TI, 2001], and does so with roughly two-thirds the energy per operation, despite being implemented in a CMOS process technology that is one generation older. Likewise, if compared to TI's fixed-point DSP, the TI C64x [Agarwala *et al.*, 2002], and normalized to the same process technology and operating voltage, *IMAGINE* sustains roughly 2.5× the peak performance at roughly the same power-efficiency [Khailany, 2003], despite having the extra overhead of floating-point arithmetic support. The next section describes the key characteristics of

the stream programming model and the following section describes stream processors in more detail.

### 2.1 Stream Programming Model

The central idea behind stream processing is to organize an application into streams and kernels to expose the inherent locality and concurrency in media-processing applications. In most cases, not only do streams and kernels expose desirable properties of media applications, but they are also a natural way of expressing the application. This leads to an intuitive programming model that maps directly to stream architectures with tens to hundreds of ALUs.

### 2.1.1 Example Application

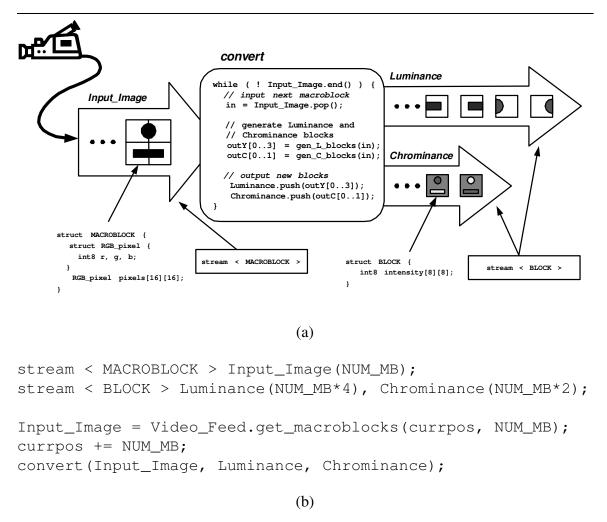

Figure 2.1 illustrates input and output streams and a kernel taken from a MPEG-2 video encoder application. Figure 2.1a shows how a kernel operates on streams graphically, while Figure 2.1b shows this process in a simplified form of StreamC, a stream programming language.

Input\_Image is a stream that consists of image data from a camera. Elements of Input\_Image are  $16 \times 16$  pixel regions, or macroblocks, on which the *convert* kernel operates. The kernel applies the same computation to the macroblocks in Input\_Image, decomposing each one into six  $8 \times 8$  blocks—four luminance blocks and two 4:1 sub-sampled chrominance blocks—and appends them to the Luminance and Chrominance output streams, respectively.

### **Streams**

As Figure 2.1a shows, streams contain a sequence of elements of the same type. Stream elements can be simple, such as a single number, or complex, such as the coordinates of a triangle in 3D space. Streams need not be the same length—for example, the Luminance stream has four times as many elements as the input stream. Further, Input\_Image could contain all of the macroblocks in an entire video frame, only a row of macroblocks from

Figure 2.1: Streams and a kernel from an MPEG-2 video encoder application. (a) The *convert* kernel translates a stream of macroblocks containing RGB pixels into streams of blocks containing luminance and chrominance pixels. (b) Textual expression of the flow of streams through kernels. The syntax is similar to that of the StreamC language. The datatype of each stream is specified within the angle brackets (< >). Kernel invocation syntax is similar to that of a regular function call in "C". The get\_macroblocks method is assumed to be defined earlier; it simply returns a consecutive number of macroblocks starting at the specified position in the stream.

the frame, or even a subset of a single row. In the stream code in Figure 2.1b, the value of NUM\_MB controls the length of the input stream.

### Kernels

The *convert* kernel consists of a loop that processes each element from the input stream. The body of the loop first pops an element from its input stream, performs some computation on that element, and then pushes the results onto the two output streams. Kernels can have one or more input and output streams and perform complex calculations ranging from a few to thousands of operations per input element—one implementation of *convert* requires 6,464 operations per input macroblock to produce the six output blocks. The only external data that a kernel can access are its input and output streams. For example, *convert* cannot directly access the data from the video feed; instead, the data must first be organized into a stream.

### **Full application**

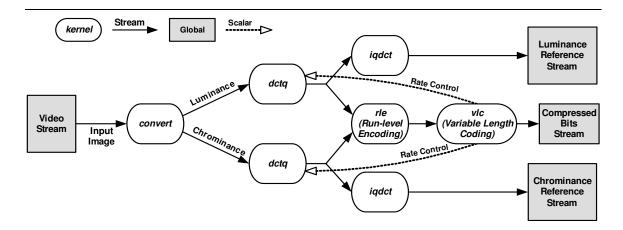

A full application, such as the MPEG-2 encoder, is composed of multiple streams and kernels. This application inputs a sequence of video images and compresses it into a single bitstream consisting of three types of frames: intra-coded, predicted, and bidirectional. The encoder compresses I-frames using only information contained in the current frame, and it compresses P- and B-frames using information from the current frame as well as additional reference frames. For example, Figure 2.2 shows one possible mapping of the portion of the MPEG-2 encoder application that encodes only I-frames into the stream processing model. Solid arrows represent data streams, and ovals represent computation kernels.

The encoder receives a stream of macroblocks (Input\_Image) from the video feed as input, and the first kernel (convert) processes this input. The discrete cosine transform (DCT) kernels then operate on the output streams produced by convert. Upon execution of all the computation kernels, the application either transmits the compressed bitstream over a network or saves it for later use. The application uses the two reference streams to compress future frames.

Figure 2.2: MPEG-2 I-frame encoder mapped to streams and kernels. The encoder receives a stream of macroblocks from a frame in the video feed as input, and the first kernel (convert) processes these. The discrete cosine transform (DCT) kernels then operate on the output streams produced by convert. Q=quantization; IQ=inverse quantization.

### 2.1.2 Locality and Concurrency

By making communication between computation kernels explicit, the stream-processing model exposes both the locality and concurrency inherent in media-processing applications. The model exposes locality by organizing communication into three distinct levels:

- *Local*. Temporary results that only need to be transferred between scalar operations within a kernel use local communication mechanisms. For example, temporary values in gen\_L\_blocks are only referenced within *convert*. This type of communication cannot be used to transfer data between two different kernels.

- Stream. Data are communicated between computation kernels explicitly as data streams. In the MPEG-2 encoder, for example, the Luminance and Chrominance streams use this type of communication.

- Global. This level of communication is only for truly global data. This is necessary

for communicating data to and from I/O devices, as well as for data that must persist

throughout the application. For example, the MPEG-2 Iframe encoder uses this level

of communication for the original input data from a video feed and for the reference

11

frames, which must persist throughout the processing of multiple video frames in the off-chip dynamic RAM (DRAM).

By requiring programmers to explicitly use the appropriate type of communication for each data element, the stream model expresses the applications inherent locality. For example, the model only uses streams to transfer data between kernels and does not burden them with temporary values generated within kernels. Likewise, the model does not use global communication for temporary streams.

The stream model also exposes concurrency in media-processing applications at multiple levels:

- *Instruction-level parallelism (ILP)*. As in traditional processing models, the stream model can exploit parallelism between the scalar operations in a kernel function. For example, the operations in gen\_L\_blocks and gen\_C\_blocks can occur in parallel.

- Data parallelism. Because kernels apply the same computation to each element of an

input stream, the stream model can exploit data parallelism by operating on several

stream elements at the same time. For example, the model parallelizes the main loop

in convert so that multiple computation elements can each decompose a different

macroblock.

- *Task parallelism*. Multiple computation tasks, including kernel execution and stream data transfers, can execute concurrently as long as they obey dependencies in the stream graph. For example, in the MPEG-2 I-frame application, the two *dctq* kernels could run in parallel.

### 2.1.3 High-Level Stream Languages

Stream languages are used to textually code applications in the stream programming model. A language such as StreamC is used to code the flow of streams through kernels in an application, while a language such as KernelC is used to code the individual kernels. Both

of these languages are specifically covered by [Mattson, 2001]. These languages are compiled using software tools designed specifically to both process stream languages and target stream architectures [Kapasi *et al.*, 2002b; Mattson *et al.*, 2000; Mattson, 2001].

Examples of how several different applications map to the stream programming model can be found in other references: Khailany et al. discuss the mapping of a stereo depth extractor [Khailany et al., 2001; Kanade et al., 1996]; Owens et al. discuss the mapping of a polygon rendering pipeline [Owens et al., 2000] and a REYES graphics pipeline [Owens et al., 2002]; Rajagopal et al. discuss the mapping of a software defined radio [Rajagopal et al., 2002]; Rajagopal also discusses the mapping of several other wireless receiver algorithms [Rajagopal, 2004]; the mapping of the FFT algorithm is discussed in [Kapasi et al., 2002a]; and, finally, the mapping of a network packet processing IPv4 stack is described in [Rai, 2003].

### 2.2 Programmable Stream Processors

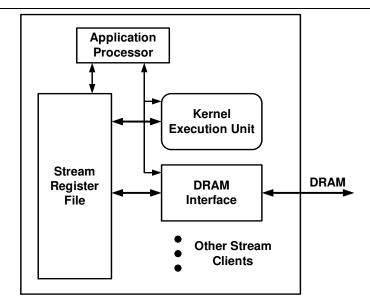

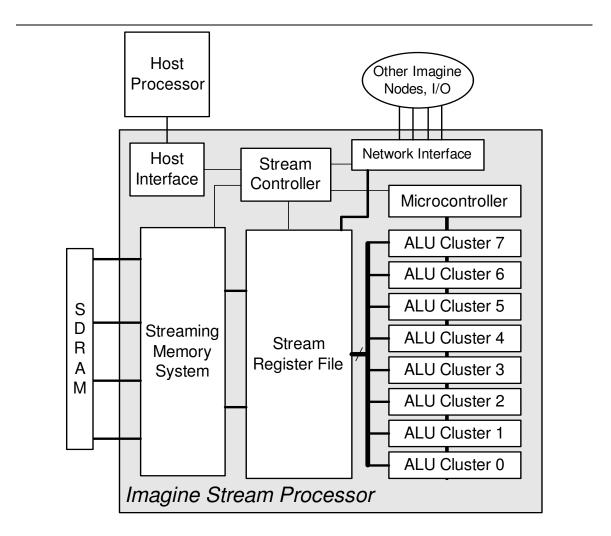

A programmable stream processor [Kapasi *et al.*, 2003; Rixner, 2001] is designed to directly execute the stream programming model we have just described. A stream processor can be implemented very efficiently by taking advantage of the locality and concurrency exposed by the stream model. Stream and kernel programs are compiled directly to such a stream processor. Figure 2.3 shows the architecture of a baseline programmable stream processor, which consists of an application processor, a stream register file, and stream clients. The SRF serves as a communication link by buffering data streams between clients, as long as the data does not exceed its storage capacity. The two stream clients in the baseline stream processor—a programmable kernel execution unit (KEU) and an off-chip DRAM interface—either consume data streams from the SRF or produce data streams to the SRF. The KEU executes kernels and provides local communication for operations within the kernels, while the off-chip DRAM interface provides access to global data storage. We will first present an ISA for this type of stream architecture, and then we will discuss the details of how we can build one efficiently in VLSI technology.

Figure 2.3: A programmable stream processor. The SRF streams data between clients—in this case the KEU, which is responsible for executing kernels and providing local communication for operations within the kernels, and the off-chip DRAM interface, which provides access to storage for global data.

### 2.2.1 Instruction Set Architecture (ISA)

The ISA of a stream processor is really composed of two unique ISAs: that of the application processor and that of the kernel execution unit. We shall describe both in turn, and then describe how they work together to execute a stream program.

### **Application Processor ISA**

The application processor executes application code like that in Figure 2.1b. The application processor's RISC-like instruction set is augmented with stream-level instructions to control the flow of data streams through the system. The application processor sequences these instructions and issues them to the stream clients, including the DRAM interface and the KEU. The DRAM interface supports two stream-level instructions—LOAD\_STREAM and STORE\_STREAM—that transfer an entire stream between off-chip DRAM and the SRF. Additional DRAM interface arguments also can specify non-contiguous access patterns, such as non-unit strides and indirect access. The programmable KEU supports two

stream-level instructions as well. The LOAD\_KERNEL instruction loads a compiled kernel function into local instruction storage within the KEU. This typically occurs only the first time a kernel is executed; on subsequent kernel invocations, the code is already available in the KEU. The RUN\_KERNEL instruction causes the KEU to start executing instructions that are encoded in its own instruction-set architecture, which is distinct from the application processor ISA.

### **Kernel Execution Unit ISA**

Instructions in the KEU ISA control the functional units and register storage within the KEU, similar to typical RISC instructions. However, unlike a RISC ISA,

- KEU instructions do not have access to arbitrary memory locations, as all external data must be read from or written to streams, and

- special communication instructions explicitly handle data-dependencies between the computations of different output elements.

The first constraint preserves locality, and the programmer ensures the constraint is met when they structure the application as a set of kernels and streams. The communication instructions make it easier to exploit concurrency on data-parallel processors, without the need to reorganize data through the memory system. These two constraints of the kernel ISA maximize stream architecture performance.

### Stream ISA

The ISA of a stream processor, or stream ISA, encapsulates both the application processor ISA and the KEU ISA. Accordingly, software tools translate high-level stream languages such as StreamC and KernelC directly to the ISA of a stream processor. For example, the *convert* kernel code shown in Figure 2.1a is compiled to the KEU ISA offline. Another compiler then compiles the application-level code shown in Figure 2.1b to the application processor ISA. The application processor executes this code and moves the precompiled kernel code to the KEU instruction memory during execution.

Assuming that the portion of the video feed the processor is encoding currently resides in DRAM memory, the three lines of application code in Figure 2.1b would result in the following sequence of operations:

The first instruction loads a portion of the raw video feed into the SRF. The second instruction is a regular scalar operation that only updates local state in the application processor. The final instruction causes the KEU to start executing the operations for the *convert* kernel. Similar instructions are required to complete the rest of the MPEG-2 I-frame application pipeline. Interestingly, a traditional compiler can only perform manipulations on simple scalar operations that tend to benefit local performance only. A stream compiler, on the other hand, can manipulate instructions that operate on entire streams, potentially leading to greater performance benefits.

To be a good compiler target for high-level stream languages, the stream processor's ISA must express the original program's locality and concurrency. To this end, three distinct address spaces in the stream ISA support the three types of communication that the stream model uses. The ISA maps local communication within kernels to the address space of the local registers within the KEU, stream communication to the SRF address space, and global communication to the off-chip DRAM address space. To preserve the stream models locality and concurrency, the processors ISA also exploits the three types of parallelism. To exploit ILP, the processor provides multiple functional units within the KEU. Because a kernel applies the same function to all stream elements, the compiler can exploit data parallelism using loop unrolling and software pipelining on kernel code. The KEU can exploit additional data parallelism using parallel hardware. To exploit task parallelism, the processor supports multiple stream clients connected to the SRF.

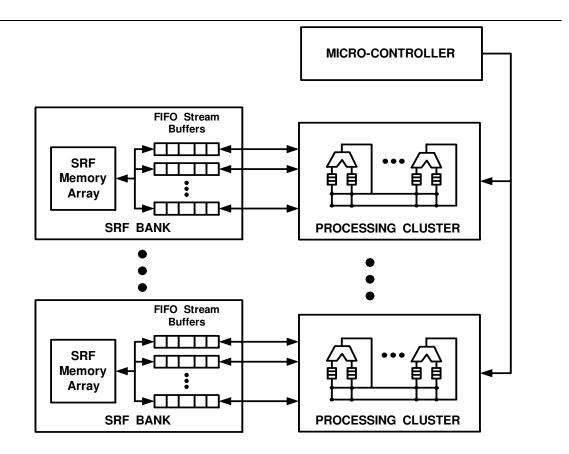

Figure 2.4: The architecture of an example kernel execution unit. There are several clusters organized in a SIMD fashion. Each cluster consists of five symmetric ALUs—i.e., they can all perform the exact same arithmetic operations. Also, there is a dedicated SRF bank for each processing cluster.

### 2.2.2 Micro-Architecture

Since we are focusing on kernel performance in this dissertation, it is worthwhile discussing the architecture of the KEU and SRF in slightly more detail. In particular, we will discuss several architectural optimizations we can apply that result in little to no performance loss since they exploit properties exposed by the stream model. Figure 2.4 shows the architecture of an example KEU.

### **Local Register Files (LRFs)**

Each processing cluster is a VLIW engine that is built to take advantage of the ILP within kernel functions. All the ALUs are the same, and each ALU supports every floating point and fixed point arithmetic operation in the kernel ISA. Notice that our first optimization is to split the register files into an SRF and cluster LRFs. This relieves the LRFs from supporting the large capacity necessary for hiding memory latency. This maps well to the stream model, which explicitly captures the locality of all the intermediate values in a kernel. Also, each ALU has a register file dedicated to each of its inputs. The outputs of the ALUs are connected to the inputs of the register files by a fully connected switch. This *distributed* register file structure improves the VLSI implementation of a processing cluster by providing small two-ported register files, instead of a single large register file with ports for all the ALUs. [Rixner *et al.*, 2000]. Not shown are additional specialized functional units, that provide interfaces to modules such as a scratch-pad register file and the inter-cluster communication switch.

### **Multiple SIMD clusters**

As shown in Figure 2.4, we have split the ALUs on a stream processor into multiple clusters, where each cluster operates on a different data element. When necessary, clusters can communicate with each other via an inter-cluster switch (not shown in figure). This might be required, for example, in order to obtain the data from neighboring clusters for a FIR filter. This cluster partitioning is done largely because a monolithic VLIW processing structure starts to become inefficient as we scale to higher numbers of ALUs [Khailany et al., 2003]. Fortunately, the cluster partitioning doesn't significantly impact performance since data-parallelism is exposed by the stream model and is readily available in media processing applications. For example, Rixner previously reported that over a range of media processing kernels, an average speedup of 7.4× was achieved on eight parallel processing clusters compared to a single cluster [Rixner et al., 1998].

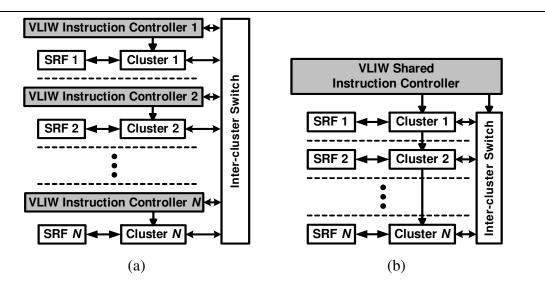

There are several options for how the clusters on a stream processor are controlled. The two extremes in the space are multiple-instruction multiple-data (MIMD) execution and single-instruction multiple-data (SIMD) execution. The KEU organizations for these

Figure 2.5: This figure shows two ways to organize the KEU in a stream architecture. The organization for the MIMD execution model is shown in (a), while the organization for the SIMD execution model is shown in (b). Other modules such as the application processor and memory system are not shown. In both organizations, each processing cluster operates on a different batch of stream elements in parallel. Notice that we are assuming that the SRF can be independently addressed by each cluster, even in the SIMD model.

two execution models are depicted graphically in Figure 2.5. In both models, every cluster executes a kernel on its own local batch of data. The differentiating feature is the independence of the VLIW instruction streams for each cluster. In the MIMD model every cluster can be executing a different instruction and a different kernel at any given time. In the SIMD model a single instruction controller issues exactly the same instructions to every processing cluster. With only a single controller, there is only one instruction stream and program counter (PC), and thus one control-flow. Therefore, the MIMD model is more flexible when each cluster wants to execute a different control-flow, a situation that arises due to kernel conditionals.

As shown in the figure, however, the MIMD model requires a separate VLIW instruction controller in return for this added flexibility. Furthermore, since large memory structures can only efficiently support a small set of independent ports, each kernel instruction memory can only serve a small set of clusters (most likely only one cluster). The impact of this extra hardware on the area of the KEU and SRF was evaluated using Khailany's

analytical models [Khailany et al., 2003]. For an eight cluster machine with a layout similar to the *IMAGINE* processor (Appendix A), the models indicate that the area of the KEU and SRF would be  $1.6 \times$  larger for a MIMD organization compared to a SIMD one. Not only does the MIMD option require more area, but it also increases the complexity in the design of the processor. For example, to support the MIMD model we would have to provide either multiple application processors (one per instruction controller), or burden a single application processor with both issuing operations to all the instruction controllers and synchronizing them.

Due to this area and complexity penalty, we would prefer to use a SIMD organization. Fortunately, this choice would not degrade the performance of any kernels that do not use conditionals. However, as we show in the next chapter, efficiently executing kernels with conditionals on SIMD organizations has been a challenge historically. Our new solutions will address this problem later in the thesis, thus allowing us to use the more area-efficient SIMD model without much performance loss across a large variety of kernels.

### **SRF Banking**

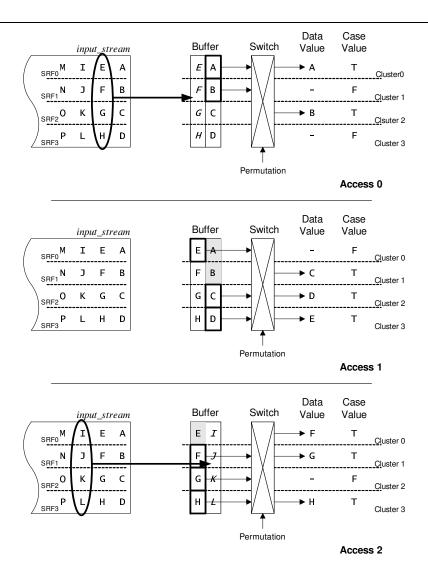

As explained in [Rixner *et al.*, 2000], the architecture of the SRF incorporates two important optimizations: banking and stream buffer FIFOs. Banking ensures that each processing cluster connects only to its own local SRF bank in order to read and write stream elements. This is done in order to reduce the number of access ports necessary for the SRF memory array, which in turn reduces the number of internal communication paths in the SRF. This partitioning matches the data-parallelism in stream programming model well, since each cluster will operate on a different stream element. Therefore, during the execution of a kernel each cluster processes the set of elements that are in its own local SRF. Any sharing of stream elements between clusters, though, requires communication over the inter-cluster switch.

### **Stream Buffers**

The second optimization, stream buffers, are added to further reduce the number of ports into the SRF memory arrays. The stream buffers are FIFOs that aggregate multiple accesses into one wide SRF memory array access. For example, consider an input stream, which transfers data from the SRF to the clusters. First the SRF will transfer a *wide* word, say 128 bits, from the SRF into the stream buffer FIFO. Then the processing cluster can read out each 32-bit word one by one from the stream buffer without requiring any more SRF memory array accesses. In this way, many stream buffers, each of which corresponds to a different logical stream in the kernel program, can time-multiplex a single port into the memory array. Like SRF banking, this also reduces the number of necessary internal communication paths in the SRF. This optimization also matches the stream programming model well, since kernels can only read or write streams in order, thereby providing sufficient spatial locality for the stream buffers to exploit.