## THE VLSI IMPLEMENTATION AND EVALUATION OF AREA- AND ENERGY-EFFICIENT STREAMING MEDIA PROCESSORS

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> Brucek Khailany June 2003

© Copyright by Brucek Khailany 2003 All Rights Reserved I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

> William J. Dally (Principal Adviser)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Mark Horowitz

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Teresa Meng

Approved for the University Committee on Graduate Studies.

## Abstract

Media applications such as image processing, signal processing, and graphics require tens to hundreds of billions of arithmetic operations per second of sustained performance for real-time application rates, yet also have tight power constraints in many systems. For this reason, these applications often use special-purpose (fixed-function) processors, such as graphics processors in desktop systems. These processors provide several orders of magnitude higher performance efficiency (performance per unit area and performance per unit power) than conventional programmable processors.

In this dissertation, we present the VLSI implementation and evaluation of stream processors, which reduce this performance efficiency gap while retaining full programmability. *Imagine* is the first implementation of a stream processor. It contains 48 32-bit arithmetic units supporting floating-point and integer data-types organized into eight SIMD arithmetic clusters. Imagine executes applications stream programs consisting of a sequence of computation kernels operating on streams of data records. The prototype Imagine processor is a 21-million transistor chip, implemented in a 0.15 micron CMOS process. At 232 MHz, a peak performance of 9.3 GFLOPS is achieved while dissipating 6.4 Watts with a die size measuring 16 mm on a side.

Furthermore, we extend these experimental results from Imagine to stream processors designed in more area- and energy-efficient custom design methodologies and to future VLSI technologies where thousands of arithmetic units on a single chip will be feasible. Two techniques for increasing the number of arithmetic units in a stream processor are presented: intracluster and intercluster scaling. These scaling techniques are shown to provide high performance efficiencies to tens of ALUs per cluster and to hundreds of arithmetic clusters, demonstrating the viability of stream processing for many years to come.

## Acknowledgments

During the course of my studies at Stanford University, I have been fortunate to work with a number of talented individuals. First and foremost, thanks goes to my research advisor, Professor William J. Dally. Through his vision and leadership, Bill has always been an inspiration to me and everyone else on the Imagine project. He also provided irreplacable guidance for me when I needed to eventually find a dissertation topic. Professor Dally provided me with the opportunity to take a leadership role on the VLSI implementation of the Imagine processor, an invaluable experience for which I will always be grateful. I would also like to thanks the other members of my reading committee, Professor Mark Horowitz and Professor Teresa Meng, for their valuable feedback regarding the work described in this dissertation and interactions over my years at Stanford.

The Imagine project was the product of the hard work of many graduate students in the Concurrent VLSI Architecture group at Stanford. Most notably, I would like to thank Scott Rixner, Ujval Kapasi, John Owens, and Peter Mattson. Together, we formed a team that took the Imagine project from a research idea to a working silicon prototype. More recently, Jung-Ho Ahn, Abhishek Das, and Ben Serebrin have helped with laboratory measurements. Thanks also goes to all of the other team members who helped with the Imagine VLSI implementation, including Jinyung Namkoong, Brian Towles, Abelardo Lopez-Lagunas, Andrew Chang, Ghazi Ben Amor, and Mohamed Kilani.

I would also like to thank all of the other members of the CVA group at Stanford, especially my officemates over the years: Ming-Ju Edward Lee, Li-Shiuan Peh, and Patrick Chiang. Many thanks also goes to Pamela Elliot and Shelley Russell, the CVA group administrators while I was a graduate student here.

The research described in this dissertation would not have been possible without the

generous funding provide by a number of sources. I would like to specifically thank the Intel Foundation for a one-year fellowship in 2001-2002 to support this research. The remainder of my time as a graduate student, I was supported by the Imagine project, which was funded by the Defense Advanced Research Projects Agency under ARPA order E254 and monitored by the Army Intelligence Center under contract DABT63-96-C0037, by ARPA order L172 monitored by the Department of the Air Force under contract F29601-00-2-0085, by Intel Corporation, by Texas Instruments, and by the Interconnect Focus Center Program for Gigascale Integration under DARPA Grant MDA972-99-1-0002.

Finally, I can not say enough about the support provided by my friends and family. My parents, Asad (the first Dr. Khailany) and Laura, have been my biggest supporters and for that I am forever grateful. Now that they will no longer be able to ask me when my thesis will be done we will have to find a new subject to discuss on the telephone. My sister and brother, Raygar and Sheilan, have always providing timely encouragement and advice. To all of my friends and family members who have helped me in one way or another over the years, I would like to say thanks.

# Contents

| A | Abstract |           |                                                             |    |  |

|---|----------|-----------|-------------------------------------------------------------|----|--|

| A | cknov    | vledgme   | ents                                                        | v  |  |

| 1 | Intr     | roduction |                                                             |    |  |

|   | 1.1      | Contri    | butions                                                     | 3  |  |

|   | 1.2      | Outlin    | e                                                           | 3  |  |

| 2 | Bac      | kground   | 1                                                           | 5  |  |

|   | 2.1      | Media     | Applications                                                | 5  |  |

|   |          | 2.1.1     | Compute Intensity                                           | 6  |  |

|   |          | 2.1.2     | Parallelism                                                 | 7  |  |

|   |          | 2.1.3     | Locality                                                    | 8  |  |

|   | 2.2      | VLSI      | Technology                                                  | 8  |  |

|   | 2.3      | Media     | Processing                                                  | 9  |  |

|   |          | 2.3.1     | Special-purpose Processors                                  | 10 |  |

|   |          | 2.3.2     | Microprocessors                                             | 11 |  |

|   |          | 2.3.3     | Digital Signal Processors and Programmable Media Processors | 13 |  |

|   |          | 2.3.4     | Vector Microprocessors                                      | 13 |  |

|   |          | 2.3.5     | Chip Multiprocessors                                        | 14 |  |

|   | 2.4      | Stream    | Processing                                                  | 15 |  |

|   |          | 2.4.1     | Stream Programming                                          | 15 |  |

|   |          | 2.4.2     | Stream Architecture                                         | 16 |  |

|   |          | 2.4.3     | Stream Processing Related Work                              | 20 |  |

|   |     | 2.4.4   | VLSI Efficiency of Stream Processors | 21 |

|---|-----|---------|--------------------------------------|----|

| 3 | Ima | gine: M | licroarchitecture and Circuits       | 26 |

|   | 3.1 | Instruc | ction Set Architecture               | 27 |

|   |     | 3.1.1   | Stream-Level ISA                     | 27 |

|   |     | 3.1.2   | Kernel-Level ISA                     | 28 |

|   |     | 3.1.3   | Kernel Instruction Format            | 31 |

|   | 3.2 | Microa  | architecture                         | 31 |

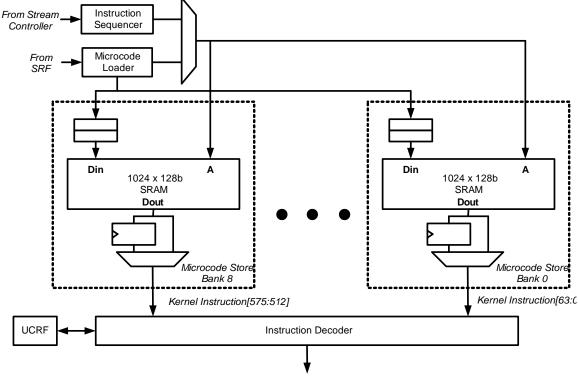

|   |     | 3.2.1   | Microcontroller                      | 32 |

|   |     | 3.2.2   | Arithmetic Clusters                  | 34 |

|   |     | 3.2.3   | Kernel Execution Pipeline            | 36 |

|   |     | 3.2.4   | Stream Register File                 | 39 |

|   |     | 3.2.5   | SRF Pipeline                         | 39 |

|   |     | 3.2.6   | Streaming Memory System              | 40 |

|   |     | 3.2.7   | Network Interface                    | 41 |

|   |     | 3.2.8   | Stream Controller                    | 42 |

|   | 3.3 | Arithn  | netic Cluster Function Units         | 43 |

|   |     | 3.3.1   | ALU Unit                             | 43 |

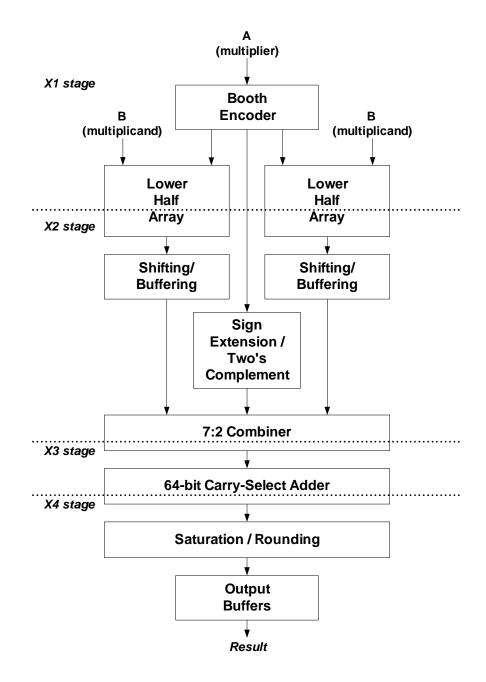

|   |     | 3.3.2   | MUL Unit                             | 46 |

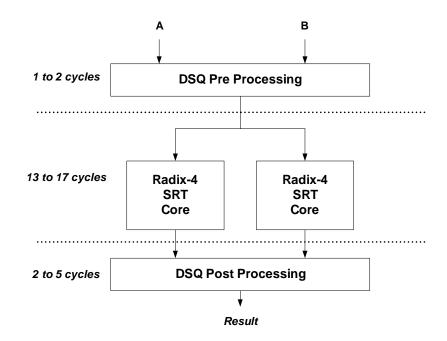

|   |     | 3.3.3   | DSQ Unit                             | 49 |

|   |     | 3.3.4   | SP Unit                              | 50 |

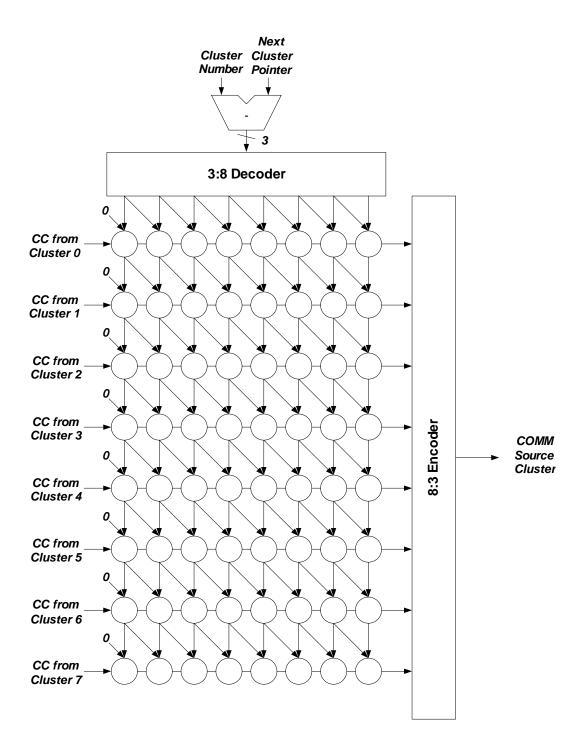

|   |     | 3.3.5   | COMM Unit                            | 50 |

|   |     | 3.3.6   | JB/VAL Unit                          | 50 |

|   | 3.4 | Summ    | ary                                  | 54 |

| 4 | Ima | gine: D | esign Methodology                    | 56 |

|   | 4.1 | Schedu  | ule                                  | 57 |

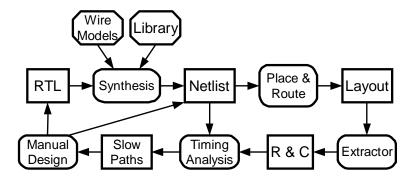

|   | 4.2 | Desigr  | n Methodology Background             | 57 |

|   | 4.3 | Imagir  | ne Design Methodology                | 59 |

|   | 4.4 | Imagir  | ne Implementation Results            | 64 |

|   | 4.5 | Imagir  | ne Clocking Methodology              | 65 |

|   | 4.6 | Imagir  | ne Verification Methodology          | 67 |

## viii

| 5 | Ima  | gine: Experimental Results            | 3                        | 69  |

|---|------|---------------------------------------|--------------------------|-----|

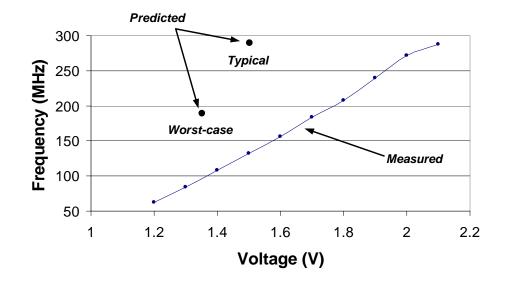

|   | 5.1  | Operating Frequency                   |                          |     |

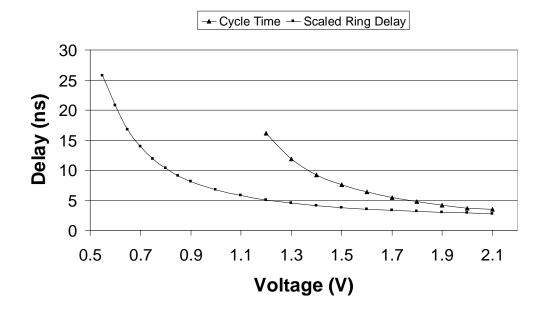

|   | 5.2  | Power Dissipation                     |                          | 73  |

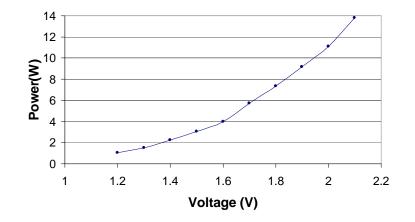

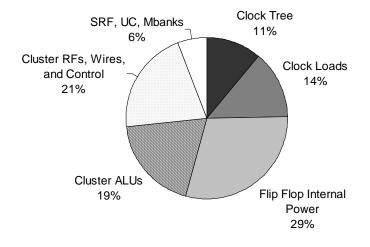

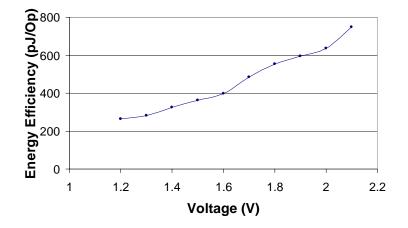

|   | 5.3  | Energy Efficiency                     |                          | 76  |

|   | 5.4  | 5.4 Sustained Application Performance |                          | 80  |

|   | 5.5  | Summary                               |                          | 81  |

| 6 | Stre | am Processor Scalability: \           | VLSI Costs               | 82  |

|   | 6.1  | VLSI Cost Models                      |                          | 84  |

|   |      | 6.1.1 Stream Processor C              | Cost Models              | 86  |

|   | 6.2  | VLSI Cost Evaluation                  |                          | 92  |

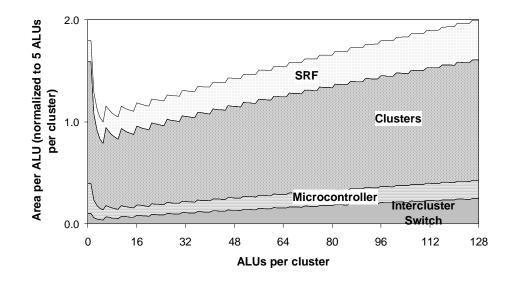

|   |      | 6.2.1 Intracluster Scaling            |                          | 92  |

|   |      | 6.2.2 Intercluster Scaling            |                          | 93  |

|   |      | 6.2.3 Combined Scaling                |                          | 94  |

|   | 6.3  | Custom and Low-Power St               | ream Processors          | 96  |

| 7 | Stre | am Processor Scalability: 1           | Performance 1            | .04 |

|   | 7.1  | Related Scalability Work              |                          | 05  |

|   | 7.2  | Technology Trends                     |                          | 06  |

|   |      | 7.2.1 Memory Bandwidt                 | h                        | 06  |

|   |      | 7.2.2 Wire Delay                      |                          | 07  |

|   | 7.3  | Performance Evaluation .              |                          | 11  |

|   |      | 7.3.1 Kernel Inner-Loop               | Performance              | 11  |

|   |      | 7.3.2 Kernel Short Stream             | n Effects                | 23  |

|   |      | 7.3.3 Application Perform             | mance                    | 26  |

|   |      | 7.3.4 Bandwidth Hierarc               | hy Scaling               | 30  |

|   | 7.4  | Improving Intercluster and            | Intracluster Scalability | 32  |

|   | 7.5  | Scalability Summary                   |                          | 36  |

| 8 | Con  | clusions                              | 1                        | .37 |

|   | 8.1  | Future Work                           |                          | 38  |

Bibliography

141

# **List of Tables**

| 2.1 | Media Processor Efficiencies (Normalized to $0.13\mu$ , $1.2 \text{ V}$ ) | 11 |

|-----|---------------------------------------------------------------------------|----|

| 3.1 | Kernel ISA - Part 1                                                       | 29 |

| 3.2 | Kernel ISA - Part 2                                                       | 30 |

| 3.3 | JB/VAL Operation for Conditional Output Streams                           | 51 |

| 3.4 | Function Unit Area and Complexity                                         | 54 |

| 4.1 | Subchip statistics                                                        | 60 |

| 4.2 | Imagine placement results                                                 | 64 |

| 4.3 | Imagine timing results                                                    | 66 |

| 5.1 | Energy-Efficiency Comparisons                                             | 77 |

| 5.2 | Energy-Delay Comparisons                                                  | 79 |

| 5.3 | Sustained Application Performance                                         | 80 |

| 6.1 | Building Block Areas, Energies, and Delays                                | 84 |

| 6.2 | Scaling Coefficients                                                      | 85 |

| 6.3 | Kernel Inner Loop Characteristics                                         | 86 |

| 6.4 | Scaling Cost Models                                                       | 89 |

| 6.5 | Building block Areas, Energies, and Delays for ASIC, CUST, and LP         | 97 |

| 6.6 | ASIC, CUST, and LP performance efficiencies                               | 98 |

| 6.7 | Technology Scaling Parameters                                             | 00 |

| 7.1 | Kernels and Applications use for Performance Evaluation                   | 12 |

| 7.2 | Intercluster Scaling Performance Efficiency                               | 22 |

# **List of Figures**

| 2.1  | A Stereo Depth Extractor                           | 6  |

|------|----------------------------------------------------|----|

| 2.2  | Stereo depth extractor as a stream program         | 16 |

| 2.3  | Stream Processor Block Diagram                     | 17 |

| 2.4  | Arithmetic Cluster Block Diagram                   | 18 |

| 3.1  | Imagine Arithmetic Cluster                         | 28 |

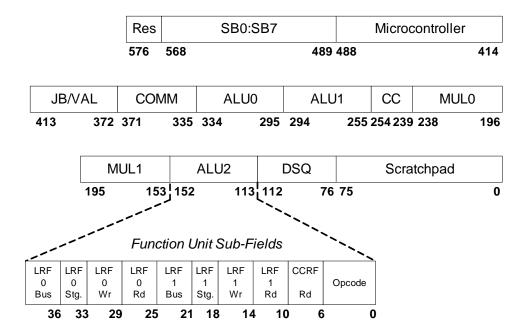

| 3.2  | VLIW Instruction Format                            | 32 |

| 3.3  | Microcontroller Block Diagram                      | 33 |

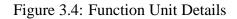

| 3.4  | Function Unit Details                              | 35 |

| 3.5  | Local Register File Implementation                 | 35 |

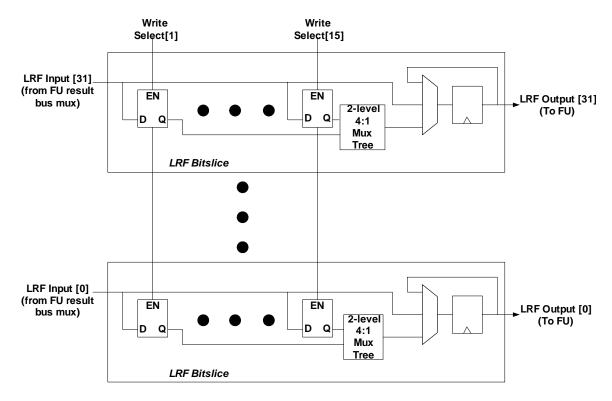

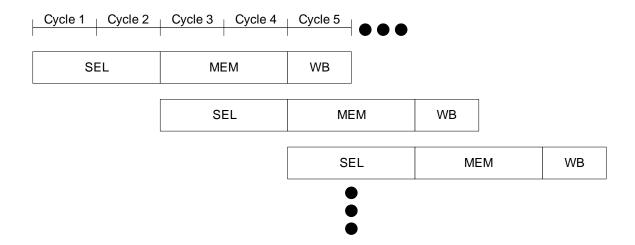

| 3.6  | Kernel Execution Pipeline Diagram                  | 37 |

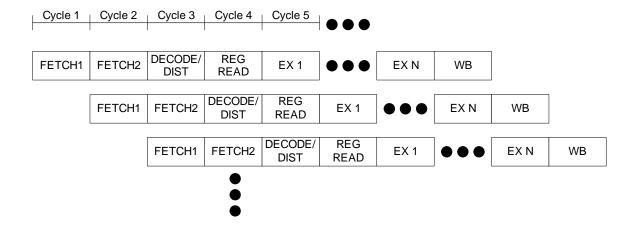

| 3.7  | Stream Register File Block Diagram                 | 38 |

| 3.8  | SRF Pipeline Diagram                               | 40 |

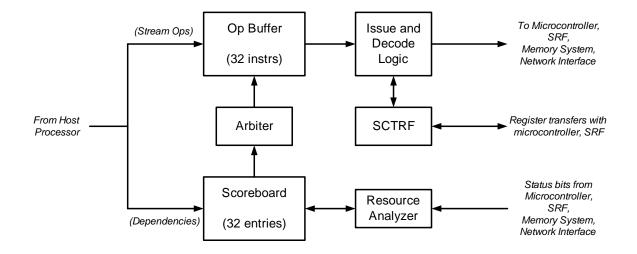

| 3.9  | Stream Controller Block Diagram                    | 42 |

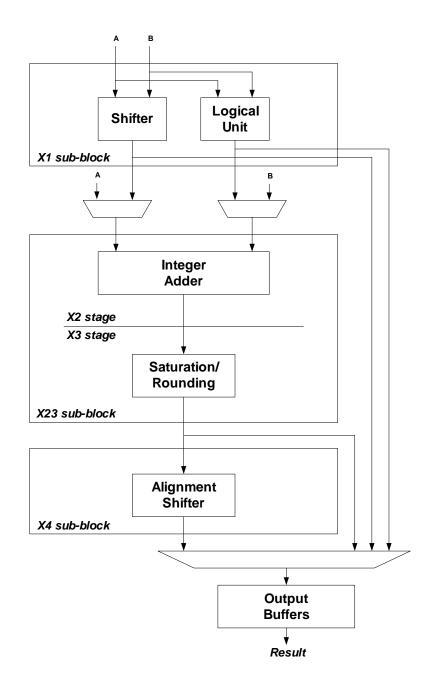

| 3.10 | ALU Unit Block Diagram                             | 45 |

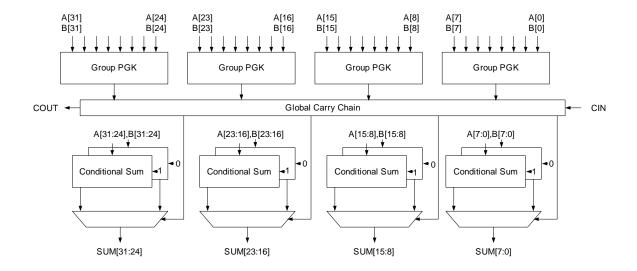

| 3.11 | Segmented Carry-Select Adder                       | 46 |

| 3.12 | MUL Unit Block Diagram                             | 47 |

| 3.13 | DSQ Unit Block Diagram                             | 49 |

| 3.14 | Computing the COMM Source Index in the JB/VAL unit | 53 |

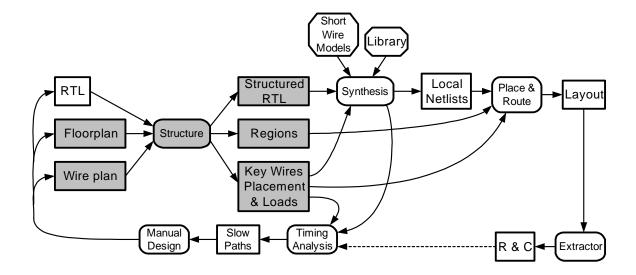

| 4.1  | Standard ASIC Design Methodology                   | 58 |

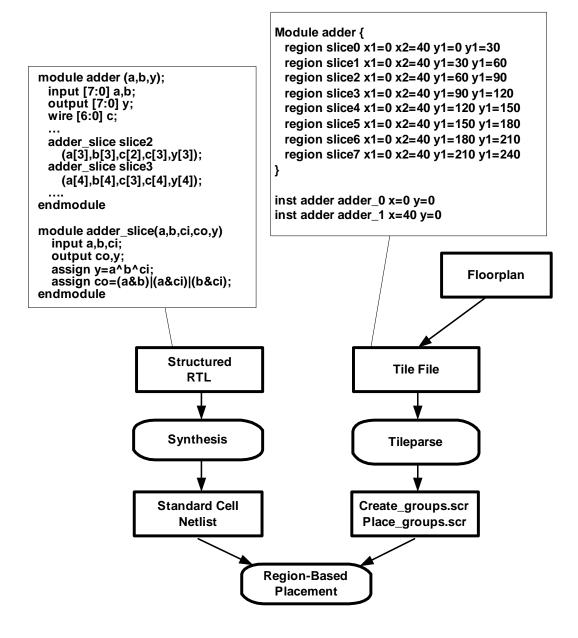

| 4.2  | Tiled Region Design Methodology                    | 61 |

| 4.3  | Tiled Region Floorplanning Details                 | 63 |

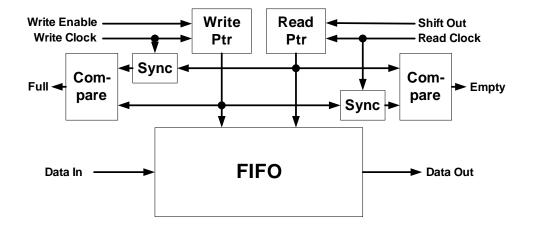

| 4.4  | Asynchronous FIFO Synchronizer                     | 67 |

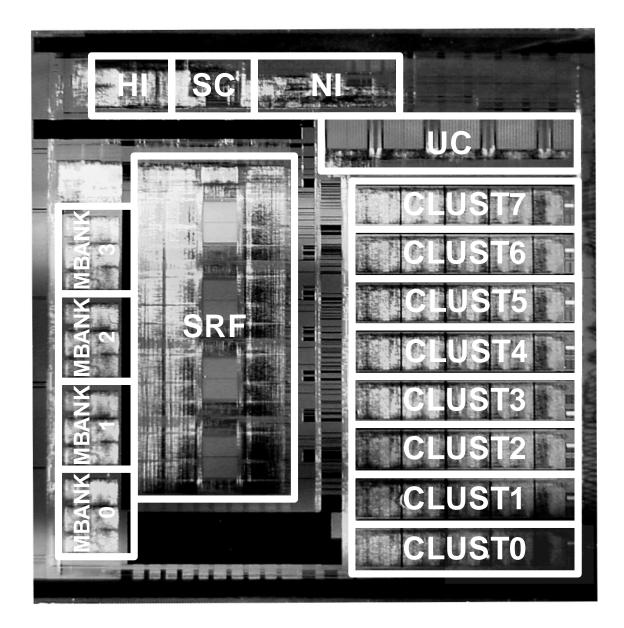

| 5.1                                                                                                                                                         | Die Photograph                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2                                                                                                                                                         | Measured Operating Frequency                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.3                                                                                                                                                         | Measured Ring Delay                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.4                                                                                                                                                         | Measured Core Power Dissipation                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.5                                                                                                                                                         | $C_{sw}$ distribution during Active Operation                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.6                                                                                                                                                         | Measured Energy Efficiency                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.1                                                                                                                                                         | Scalable Grid Floorplan                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.2                                                                                                                                                         | Intracluster Switch Floorplan                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.3                                                                                                                                                         | Area of Intracluster Scaling                                                                                                                                                                                                                                                                                                                                                                                                      |

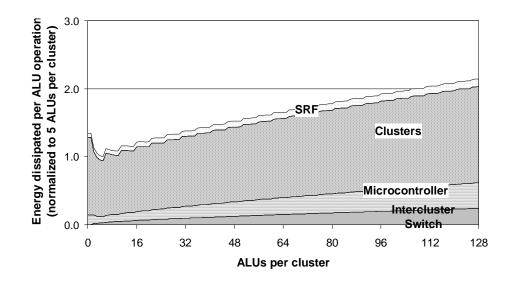

| 6.4                                                                                                                                                         | Energy of Intracluster Scaling                                                                                                                                                                                                                                                                                                                                                                                                    |

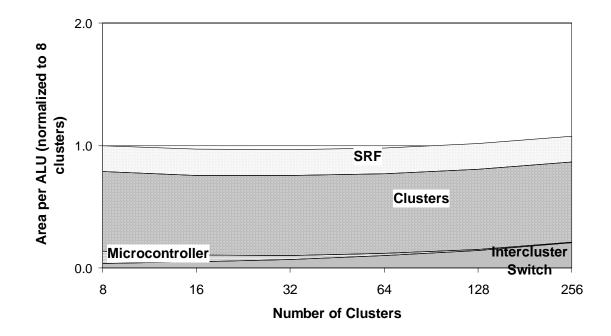

| 6.5                                                                                                                                                         | Area of Intercluster Scaling                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.6                                                                                                                                                         | Energy of Intercluster Scaling                                                                                                                                                                                                                                                                                                                                                                                                    |

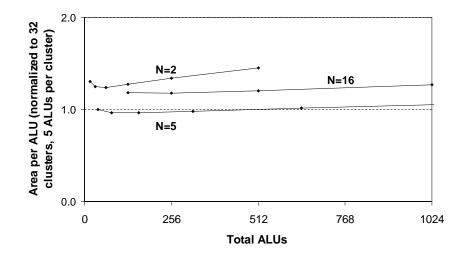

| 6.7                                                                                                                                                         | Area of Combined Scaling                                                                                                                                                                                                                                                                                                                                                                                                          |

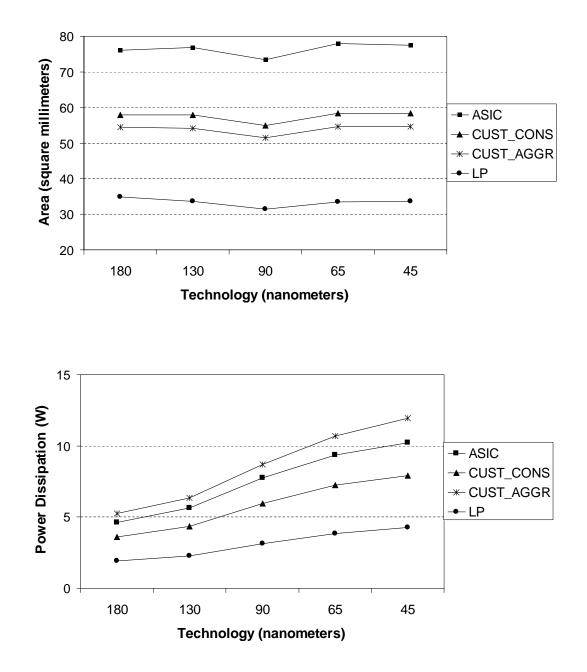

| 6.8                                                                                                                                                         | Effect of Technology Scaling on Die Area and Power Dissipation 101                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                   |

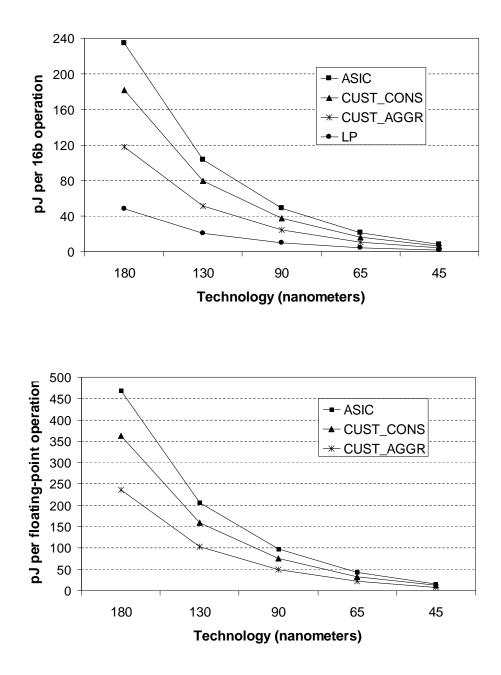

| 6.9                                                                                                                                                         | Effect of Technology Scaling on Energy Efficiency                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.9<br>7.1                                                                                                                                                  | Effect of Technology Scaling on Energy Efficiency                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                   |

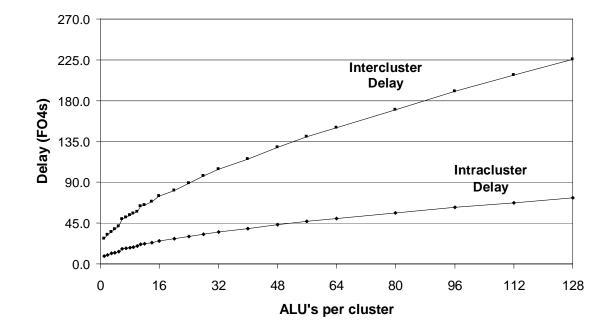

| 7.1                                                                                                                                                         | Worst-case Switch Delay with Intracluster Scaling                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.1<br>7.2                                                                                                                                                  | Worst-case Switch Delay with Intracluster Scaling                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.1<br>7.2<br>7.3                                                                                                                                           | Worst-case Switch Delay with Intracluster Scaling       108         Worst-case Switch Delay with Intercluster Scaling       109         Intracluster Scaling with no Loop Transformations       113                                                                                                                                                                                                                               |

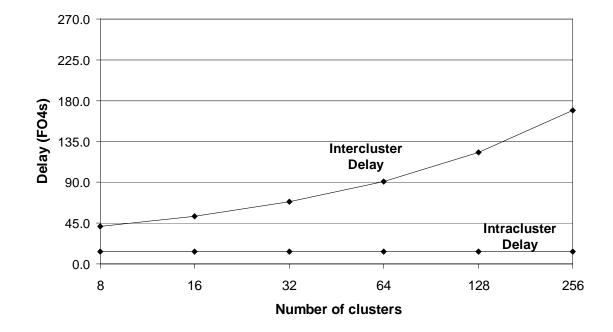

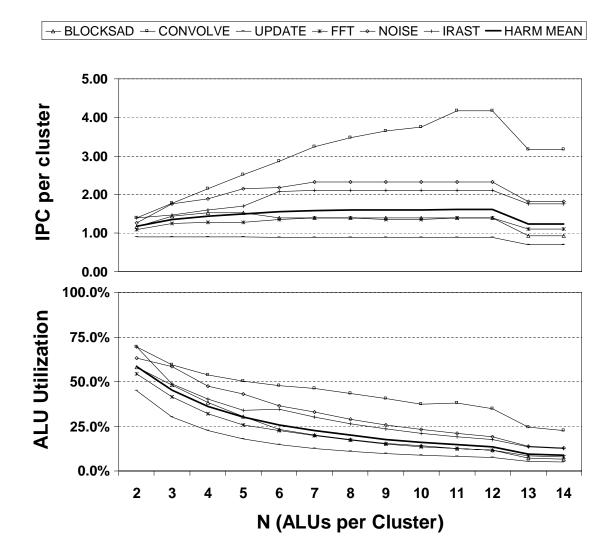

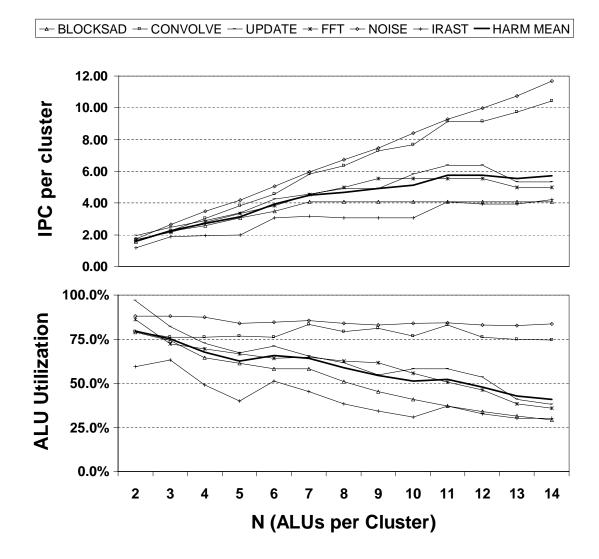

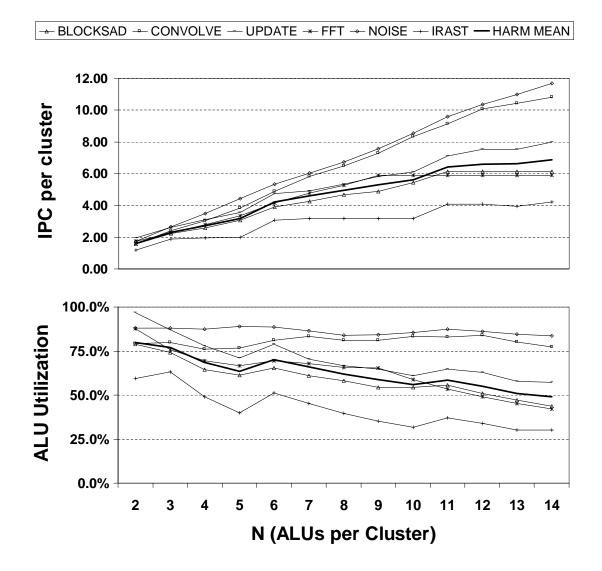

| <ol> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> </ol>                                                                                              | Worst-case Switch Delay with Intracluster Scaling       108         Worst-case Switch Delay with Intercluster Scaling       109         Intracluster Scaling with no Loop Transformations       113         Intracluster Scaling with Software Pipelining       116                                                                                                                                                               |

| <ol> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> </ol>                                                                                 | Worst-case Switch Delay with Intracluster Scaling108Worst-case Switch Delay with Intercluster Scaling109Intracluster Scaling with no Loop Transformations113Intracluster Scaling with Software Pipelining116Intracluster Scaling with Software Pipelining and Loop Unrolling118                                                                                                                                                   |

| <ol> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> </ol>                                                                    | Worst-case Switch Delay with Intracluster Scaling108Worst-case Switch Delay with Intercluster Scaling109Intracluster Scaling with no Loop Transformations113Intracluster Scaling with Software Pipelining116Intracluster Scaling with Software Pipelining and Loop Unrolling118Inner-Loop Performance per Area with Intracluster Scaling120                                                                                       |

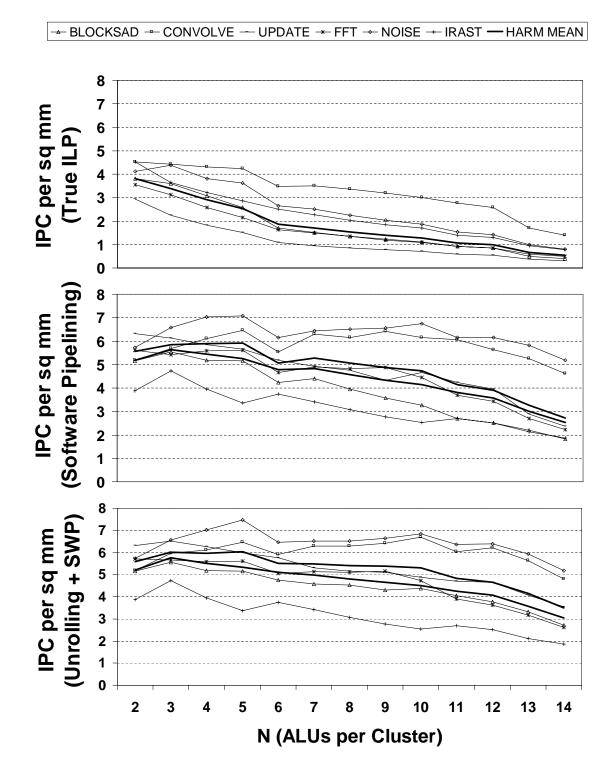

| <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> </ul>                                                       | Worst-case Switch Delay with Intracluster Scaling108Worst-case Switch Delay with Intercluster Scaling109Intracluster Scaling with no Loop Transformations113Intracluster Scaling with Software Pipelining116Intracluster Scaling with Software Pipelining and Loop Unrolling118Inner-Loop Performance per Area with Intracluster Scaling120Intercluster Kernel Speedup121                                                         |

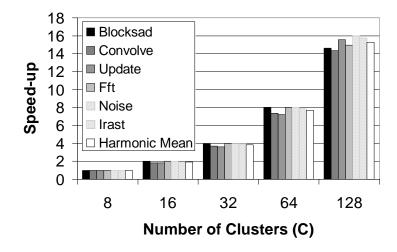

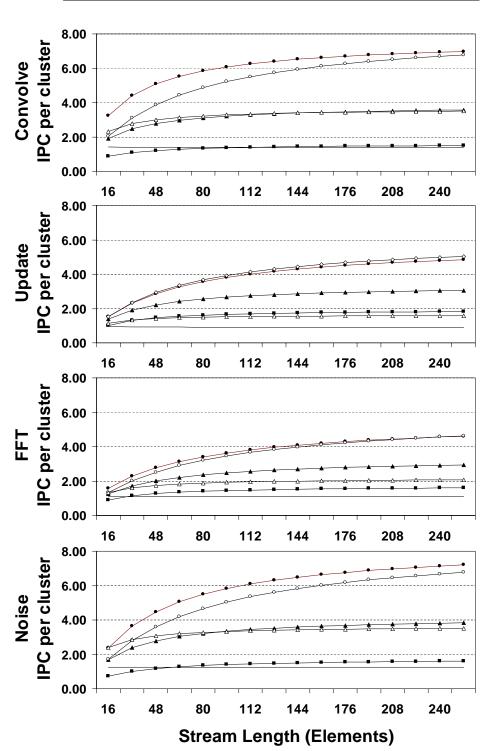

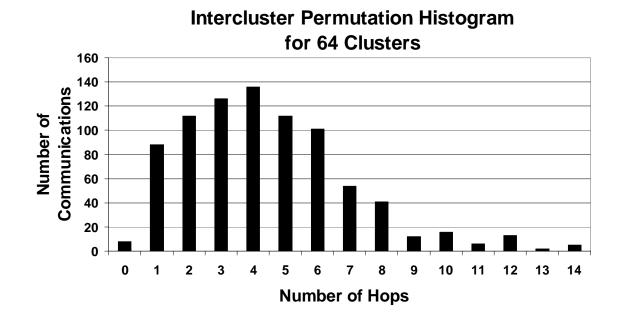

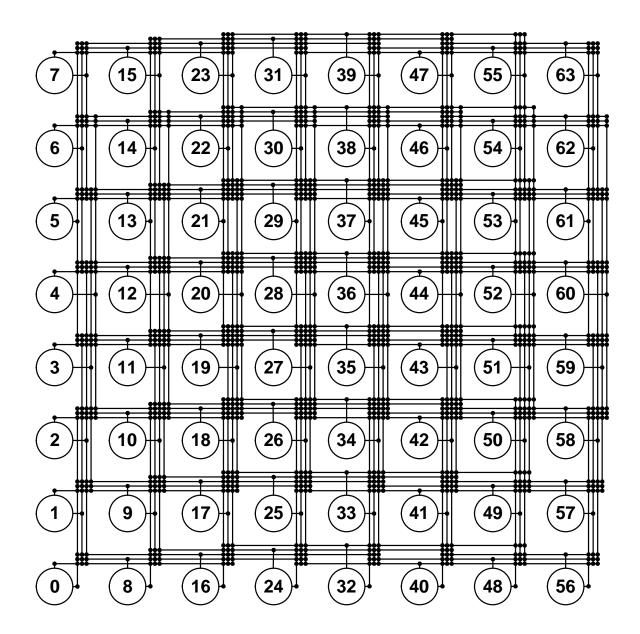

| <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> </ul>                             | Worst-case Switch Delay with Intracluster Scaling108Worst-case Switch Delay with Intercluster Scaling109Intracluster Scaling with no Loop Transformations113Intracluster Scaling with Software Pipelining116Intracluster Scaling with Software Pipelining and Loop Unrolling118Inner-Loop Performance per Area with Intracluster Scaling120Intercluster Kernel Speedup121Kernel Short Stream Effects124                           |

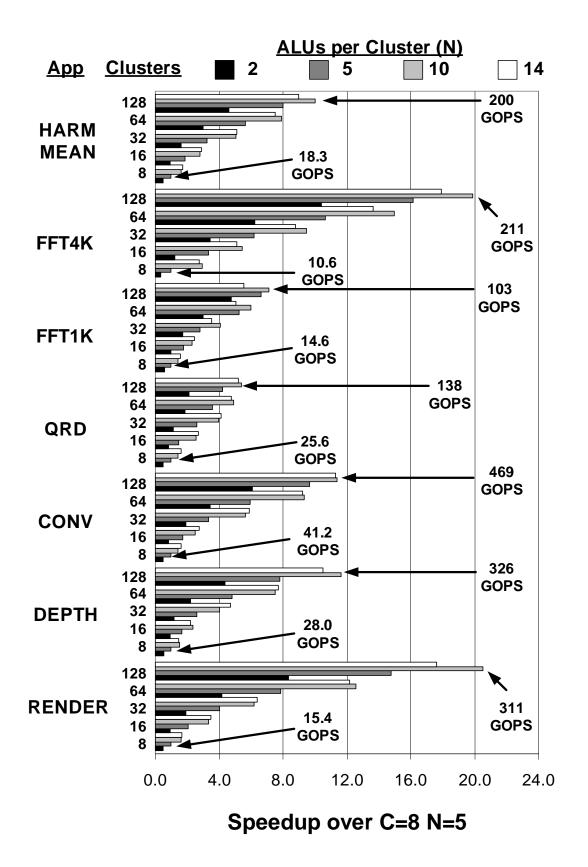

| <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> <li>7.10</li> </ul>               | Worst-case Switch Delay with Intracluster Scaling108Worst-case Switch Delay with Intercluster Scaling109Intracluster Scaling with no Loop Transformations113Intracluster Scaling with Software Pipelining116Intracluster Scaling with Software Pipelining and Loop Unrolling118Inner-Loop Performance per Area with Intracluster Scaling120Intercluster Kernel Speedup121Kernel Short Stream Effects124Application Performance127 |

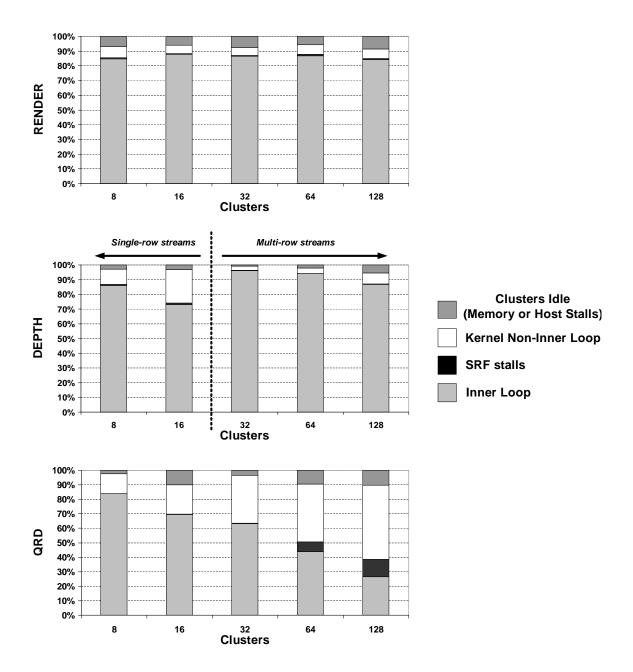

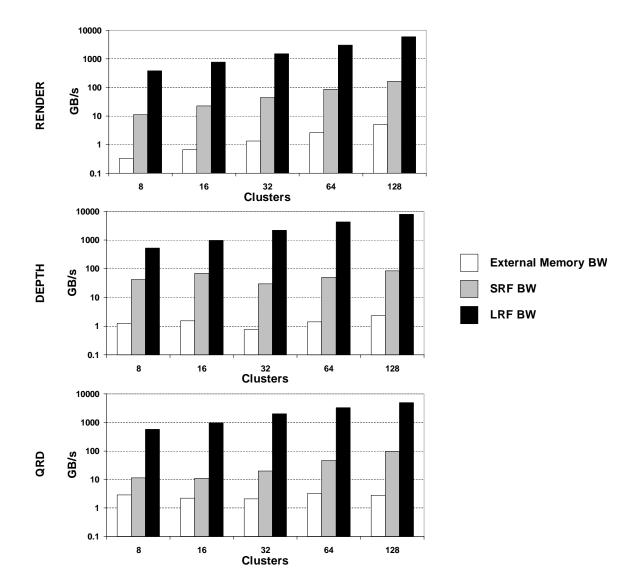

| <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> <li>7.9</li> <li>7.10</li> <li>7.11</li> </ul> | Worst-case Switch Delay with Intracluster Scaling108Worst-case Switch Delay with Intercluster Scaling109Intracluster Scaling with no Loop Transformations113Intracluster Scaling with Software Pipelining116Intracluster Scaling with Software Pipelining and Loop Unrolling118Inner-Loop Performance per Area with Intracluster Scaling120Intercluster Kernel Speedup121Kernel Short Stream Effects124Application Performance129 |

## **Chapter 1**

## Introduction

Computing devices and applications have recently emerged to interface with, operate on, and process data from real-world samples classified as *media*. As media applications operating on these data-types have come to the forefront, the design of processors optimized to operate on these applications have emerged as an important research area. Traditional microprocessors have been optimized to execute applications from desktop computing workloads. Media applications are a workload with significantly different characteristics, meaning that the potential for large improvements in performance, cost, and power efficiency can be achieved by improving media processors.

Media applications include workloads from the areas of signal processing, image processing, video encoding and decoding, and computer graphics. These workloads require a large and growing amount of arithmetic performance. For example, many current computer graphics and image processing applications in desktop systems require tens to hundreds of billions of arithmetic operations per second for real-time performance [Rixner, 2001]. As scene complexity, screen resolutions, and algorithmic complexity continues to grow, this demand for absolute performance will continue to increase. Similar examples of large and growing performance requirements can be drawn in the other application areas, such as the need for higher communication bandwidth rates in signal processing and higher video quality in video encoding and decoding algorithms. As a result, media processors must be designed to provide large amounts of absolute performance.

While high performance is necessary to meet the computational requirements of media

applications, many media processors will need to be deployed in mobile systems and other systems where cost and power consumption is a key concern. For this reason, low power consumption and high energy efficiency, or high performance per unit power (low average energy dissipated per arithmetic operation), must be a key design goal for any media processor.

Fixed-function processors have been able to provide both high performance and good energy-efficiency when compared to their programmable counterparts on media applications. For example, the Nvidia Geforce3 [Montrym and Moreton, 2002; Malachowsky, 2002], a recent graphics processor, provides 1.2 Teraops per second of peak performance at 12 Watts for an energy-efficiency of 10 picoJoules per operation. In comparison, programmable digital signal processors and microprocessors are several orders of magnitude worse in absolute performance and in energy efficiency. However, programmability is a key requirement in many systems where algorithms are too complex or change too rapidly to be built into fixed-function hardware. Using programmable rather than fixed-function processors also enables fast time-to-market. Finally, the cost of building fixed-function chips is growing significantly in deep sub-micron technologies, meaning that programmable solutions also have an inherent cost advantage since a single programmable chip can be used in many different systems. For these reasons, a programmable media processors is desirable.

Stream processors have recently been proposed as a solution that can provide all three of the above: performance, energy efficiency, and programmability. In this dissertation, the design and evaluation of a prototype stream processor, called *Imagine* is presented. This 21-million transistor processor is implemented in a 5-level metal 0.15 micron CMOS technology with a die size measuring 16 millimeters on a side. At 232 MHz, a peak performance of 9.3 GFLOPS is achieved while dissipating 6.4 Watts. Furthermore, in future VLSI technologies, the scalability of stream processors to Teraops per second of peak performance is demonstrated.

## **1.1 Contributions**

This dissertation makes several contributions to the fields of computer architecture and media processing:

- The design and evaluation of the Imagine stream processor. This is the first VLSI implementation of a stream architecture and provides experimental verification to the VLSI feasibility and performance of stream processors.

- Analysis on the performance efficiency of stream processors. This analysis demonstrates the potential for providing high performance per unit area and high performance per unit power when compared to other media processor architectures.

- Analytical models for the area, power, and delay of key components of a stream processor. These models are used to demonstrate the scalability of stream processors to thousands of arithmetic units in future VLSI technologies.

- An analysis of the performance of media applications as the number of arithmetic units per stream processor are increased. This analysis provides insights into the available parallelism in media applications and explores the tradeoffs in area, power, and performance for different methods of scaling to large numbers of arithmetic units per stream processor.

## **1.2 Outline**

Recently, media processing has gained attention in both commercial products and academic research. The important recent trends in media processing are presented in Chapter 2. One such trend which has gained prominence in the research community is stream processing. In Chapter 2, we introduce and explain stream processing, which consists of a programming model and architecture that enables high performance on media applications with fully-programmable processors.

In order to explore the performance and efficiency of stream processing, a prototype stream processor, *Imagine*, was designed and implemented in a modern VLSI technology.

In Chapter 3, the instruction set architecture, microarchitecture, and key arithmetic circuits from Imagine are described. In Chapter 4, the design methodology is presented and finally, in Chapter 5, experimental results are provided. Also in Chapter 5, the energy efficiency of Imagine and a comparison to existing processors is presented.

This work on Imagine was then extended to study the scalability of stream processors to future VLSI technologies when thousands of arithmetic units could fit on a single chip. In Chapter 6, analytical models for the area, power, and delay of key components of a stream processor are presented. These models are then used to explore how area and energy efficiency scales with the number of arithmetic units. In Chapter 7, performance scalability is studied by exploring the available parallelism in media applications and by exploring the tradeoffs between different methods of scaling.

Finally, conclusions and future work are presented in Chapter 8.

## Chapter 2

## Background

Media applications and media processors have recently become an active and important area of research. In this chapter, background and previous work on media processing is presented. First, media application characteristics and previous work on processors for running these applications is presented. Then, stream processors are introduced. Stream processors have recently been proposed as an architecture that exploits media application characteristics to achieve better performance, area efficiency, and energy efficiency than existing programmable processors.

## 2.1 Media Applications

Media applications are programs with real-time performance requirements that are used to process audio, video, still images, and other data-intensive data. Example application domains include image processing, computer-generated graphics, video encoding or decoding, and signal processing. As previous researchers have pointed out, these applications share several important characteristics: compute intensity, parallelism, and locality [Rixner, 2001].

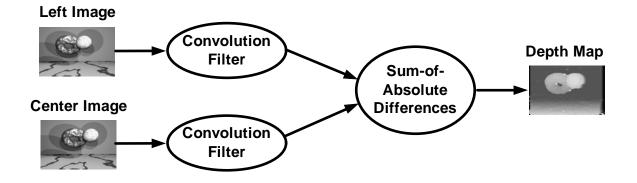

A flow-diagram representation of one such media application, a stereo depth extractor, is shown graphically in Figure 2.1 [Kanade *et al.*, 1996]. In this application, using two images offset by a horizontal disparity as input from two cameras, each row from each image is first filtered and then compared using a sum-of-absolute differences metric to

Figure 2.1: A Stereo Depth Extractor

estimate the disparity between objects in the images. From the disparity calculated at each image pixel, the depth of objects in an image can be approximated. This stereo depth extractor will be used to demonstrate the three important characteristics common to most media applications.

### 2.1.1 Compute Intensity

The first important characteristic is compute intensity, meaning that media applications require a high number of arithmetic operations per memory reference when compared to traditional desktop applications. Rixner studied application characteristics of four media applications: the stereo depth extractor presented above, a video encoder/decoder, a polygon renderer, and a matrix QR decomposition [Rixner, 2001]. On the stereo depth extractor, 473.3 arithmetic operations in the convolution filter and sum-of-absolute difference calculations were required per inherent memory reference (input, output, and other global data accesses). The other applications ranged between 57.9 and 155.3 arithmetic operations per memory reference. In comparison, traditional desktop integer applications have ratios of less than 2: arithmetic operations comprise between 2% and 50% of dynamically executed instructions whereas memory loads and stores account for 15% to 80% of instructions in the SPECint2000 benchmark suite [KleinOsowski *et al.*, 2000]. This difference suggests that architectures optimized for integer benchmarks such as general-purpose microprocessors would not be as well-suited to media applications and vice versa.

#### 2.1.2 Parallelism

Not only do these applications require large numbers of arithmetic operations per memory reference, but many of these arithmetic operations can be executed in parallel. This available parallelism in media applications can be classified into three categories: instruction-level parallelism (ILP), data-level parallelism (DLP), and task-level parallelism (TLP).

The most plentiful parallelism in media applications is at the data level. DLP refers to computation on different data elements occurring in parallel. Furthermore, DLP in media applications can often be exploited with SIMD execution since the same computation is typically applied to all data elements. For example, in the stereo depth extractor, all output pixels in the depth map could theoretically be computed in parallel by the same fixed-function hardware element since there are no dependencies between these pixels and the computation required for every pixel is the same. Other media applications also contain large degrees of DLP.

Some parallelism also is available at the instruction level. In the stereo depth extractor, ILP refers to the parallel execution of individual arithmetic instructions in the convolution filter or sum-of-absolute differences calculation. For example, the convolution filter computes the product of a coefficient matrix with a sequence of pixels. This matrix-vector product includes a number of multiplies and adds that could be performed in parallel. Such fine-grained parallelism between individual arithmetic operations operating on one data element is classified as ILP and can be exploited in many media applications. As will be shown later in Chapter 7, available ILP in media applications is usually limited to a few instructions per cycle due to dependencies between instructions. Although other researchers have shown that out-of-order superscalar microprocessors are able to execute up to 4.2 instructions per cycle on some media benchmarks [Ranganathan *et al.*, 1999], this is largely due to DLP being converted to ILP with compiler or hardware techniques rather than the true ILP that exists in these applications.

Finally, the stereo depth extractor and other media applications also contain task-level, or thread-level, parallelism. TLP refers to different stages of a computation pipeline being overlapped. For example, in the stereo depth extractor, there are four exeuction stages: load image data, convolution filter, sum-of-absolute differences, and store output data. TLP is

available in this application because these execution stages could be set up as a pipeline where each stage concurrently processes different portions of the dataset. For example, a pipeline could be set up where each stage operates on a different row: the fourth image rows are loaded from memory, the convolution filter operates on the third rows, sum-of-absolute differences is computed between the second rows, while the first output row is stored back to memory. Note that ILP, DLP, and TLP are all orthogonal types of parallelism, meaning that all three could theoretically be supported simultaneously.

### 2.1.3 Locality

In addition to compute intensity and parallelism, the other important media application characteristic is locality of reference for data accesses. This locality can be classified into kernel locality and producer-consumer locality. Kernel locality is temporal and refers to reuse of coefficients or data during the execution of computation kernels such as the convolution filter. Producer-consumer locality is also a form of temporal locality that exists between different stages of a computation pipeline or kernels. It refers to data which is *produced*, or written, by one kernel and *consumed*, or read, by another kernel and is never read again. This form of locality is seen very frequently in media applications [Rixner, 2001]. In a traditional microprocessor, kernel locality would most often be captured in a register file or a small first-level cache. Producer-consumer locality on the other hand is not as easily captured by traditional cache hierarchies in microprocessors since it is not well-matched to least-recently-used replacement policies typically utilized in caches.

## 2.2 VLSI Technology

Not only has the typical application domain for programmable processors shifted over the last decade, the technology constraints of modern VLSI (Very Large Scale Integrated Circuits) has evolved as well. In the past, gates used for computation were the critical resource in VLSI design, but in modern technology, computation is cheap and communication between computational elements is expensive. For example, in the Imagine processor [Khailany *et al.*, 2002], a single-precision floating-point multiply-accumulate unit in a

0.18  $\mu$ m technology measures 0.486  $mm^2$  and dissipates 185 pJ per multiply (0.185 mW per MHz). A thousand of these multipliers could fit on a single die in a 0.13  $\mu$ m technology.

While arithmetic itself is cheap, handling the data and control communication between arithmetic units is expensive. On-chip communication between such arithmetic units requires storage and wires. Small distributed storage elements are not too expensive compared to arithmetic. In the same 0.18  $\mu$ m technology, a 16-word 32-bit, one-read-port one-write-port SRAM which is 0.0234  $mm^2$  and dissipates 15pJ per access cycle assuming both ports are active. However, as additional ports are added to this memory, the area cost increases significantly. Furthermore, the drivers and wires for a 32-bit 5 millimeter bus dissipate 24 pJ per transfer on average [Ho *et al.*, 2001]. If each multiply requires three multi-ported memory accesses and three 5 millimeter bus transfers (two reads and one write), then the cost of the communication is very similar to the cost of a multiply. Architectures must therefore manage this communication effectively in order to keep its area and energy costs from dominating the computation itself. Off-chip communication is an even more critical resource, since there are only hundreds of pins available in large chips today. In addition, each off-chip communication dissipates a lot of energy (typically over 1 nJ for a 32b transfer) when compared to arithmetic operations.

Although handling the cost of communication in modern VLSI technology is a challenge, media application characteristics are well-suited to take advantage of cheap computation with highly distributed storage with local communications. Cheap computation can be exploited with large numbers of arithmetic units to take advantage of both compute intensity and parallelism in these applications. Furthermore, producer-consumer locality can be exploited to keep communication local as much as possible, thereby minimizing communication costs.

## 2.3 Media Processing

Processors can exploit application characteristics to provide both high performance and more importantly, performance efficiency. High performance efficiency implies a high ratio of performance per unit area, *area efficiency*, and a high ratio of performance per unit power, *energy or power efficiency*. These metrics are often more important than raw performance in many media processing systems since higher area efficiency leads to low cost and better manufacturability, both important in embedded systems. Energy efficiency implies that for executing a fixed computation task, less energy from a power source such as a battery is used, leading to longer battery life and lower packaging costs in mobile products. In this section, we present previous work on fixed-function and programmable processors for media applications, with data on both performance and performance efficiency.

#### 2.3.1 Special-purpose Processors

Special-purpose, or fixed-function, processors directly map an application's data-flow graph into hardware and can therefore exploit important application characteristics. They contain a large number of computation elements operating in parallel, exploiting both the compute intensity and parallelism in media applications. These computation blocks are then connected together by dedicated wires and memories, exploiting available producer-consumer locality. Using dedicated wires and memories for local storage near the computation elements is very area- and energy-efficient, since it minimizes traversals of long on-chip wires and accesses to large global multi-ported memories. As a result, a large percentage of die area and active power dissipation is allocated to the computation elements rather than control and communication structures.

An energy-efficiency comparison between a variety of fixed-function and programmable processors for media applications is shown in Table 2.1. All processors have been normalized to a 0.13 micron, 1.2 Volt technology. Energy efficiency is shown as energy per arithmetic operation and is calculated from peak performance and power dissipation. Although most processors sustain a fraction of peak performance on most applications, sustained performance and power dissipation measurements are not widely available, so peak numbers are used here.

The energy efficiency of two special-purpose media processors are listed in the first section of Table 2.1. A polygon rendering chip, the Nvidia Geforce3 [Montrym and More-ton, 2002; Malachowsky, 2002], and a MPEG4 [Ohashi *et al.*, 2002] video decoder are presented. These processors provide energy efficiencies of better than 6 pJ per arithmetic

| Processor         | Data-type | Peak Perf   | Power  | Energy/Op |

|-------------------|-----------|-------------|--------|-----------|

| Nvidia GeForce3   | 8-16b     | 1200 GOPS   | 6.7 W  | 5.5 pJ    |

| MPEG4 Decode      | 8-16b     | 2 GOPS      | 6.2 mW | 3.2 pJ    |

| Intel Pentium 4   | FP        | 12 GFLOPS   | 51.2 W | 4266 pJ   |

| (3.08 GHz)        | 16b       | 24 GOPS     | 51.2 W | 2133 pJ   |

| SB-1250           | FP        | 12.8 GFLOPS | 8.7 W  | 677 pJ    |

| (800 MHz)         | 64b       | 6.4 GOPS    | 8.7 W  | 1354 pJ   |

|                   | 16b       | 12.8 GOPS   | 8.7 W  | 677 pJ    |

| TI C67x (225 MHz) | FP        | 1.35 GFLOPS | 1.2 W  | 889 pJ    |

| TI C64x (600 MHz) | 16b       | 4.8 GOPS    | 720 mW | 150 pJ    |

| VIRAM             | FP        | 1.6 GFLOPS  | 1.4 W  | 875 pJ    |

|                   | 16b       | 9.6 GOPS    | 1.4 W  | 146 pJ    |

Table 2.1: Media Processor Efficiencies (Normalized to  $0.13\mu$ , 1.2 V)

operation when normalized to a 0.13  $\mu$ m technology. The other processors in Table 2.1 are all programmable. Although area efficiencies are not provided in the table, comparisons between processors for energy efficiency should be similar to area efficiency. As can be seen, there is an efficiency gap of several orders of magnitude between the special-purpose and programmable processors. The remainder of this section will provide background into these programmable processors and explain their performance efficiency limitations.

### 2.3.2 Microprocessors

The second section of Table 2.1 includes two microprocessors, a 3.08 GHz Intel Pentium 4<sup>1</sup> [Sager *et al.*, 2001; Intel, 2002] and a SiByte SB-1250, which consists of two on-chip SB-1 CPU cores [Sibyte, 2000]. The Pentium 4 is designed for high performance through deep pipelining and high clock rate. The SiByte processor is targeted specifically for energy efficient operation through extensive use low power design techniques, and has efficiencies similar to other low power microprocessors, such as XScale [Clark *et al.*, 2001]. These

<sup>&</sup>lt;sup>1</sup>Gate length for this process is actually 60-70 nanometers because of poly profiling engineering [Tyagi *et al.*, 2000; Thompson *et al.*, 2001].

processors demonstrate the range of energy efficiencies typically provided by microprocessors, over 500 pJ per instruction when normalized to a 0.13 micron technology.

Microprocessors have markedly lower efficiencies than special-purpose processors because of deep pipelining and because of the large amount of area and power taken up by control structures and large global memories such as caches. For example, less than 15% of die area in the Pentium 3 [Green, 2000], the predecessor to the Pentium 4, is devoted to the arithmetic execution units. In addition, deep pipelining with over 20 pipeline stages, used in the Pentium 4, requires high clock power, large branch predictors, and speculative hardware in order to achieve high performance at the expense of energy efficiency. The Sibyte processor is limited to more modest pipeline lengths for energy efficiency, but still is based around an architecture with a global register file and global communications through a cache hierarchy. Caches in microprocessors are not optimized to directly take advantage of producer-consumer locality to increase available on-chip bandwidth, but rather are optimized to exploit temporal and spatial locality to reduce average memory latency.

In addition to energy inefficiencies in control structures, pipelining, and caches, existing microprocessor architectures are unable to take advantage of the compute intensity or parallelism in media applications. A single unified multi-ported register file does not scale efficiently to tens of arithmetic units, limiting the compute intensity and parallelism that can be exploited. Furthermore, microprocessors are mainly optimized to exploit ILP, less plentiful than the highly available DLP in media applications. Recently, microprocessors have tried to exploit DLP to achieve higher performance and to overcome register file scalability limitations by adding SIMD extensions to their instruction sets. Some example ISA extensions include VIS [Tremblay *et al.*, 1996], MAX-2 [Lee, 1996], MMX [Peleg and Weiser, 1996], Altivec [Phillip, 1998], SSE [Thakkar and Huff, 1999], and others. However, the amount of data parallelism exploited by SIMD extensions is limited to the width of SIMD arithmetic units, typically less than 4 parallel data elements. This means each SIMD instruction can only capture a small percentage of the DLP available in media applications [Kozyrakis, 2002].

#### **2.3.3 Digital Signal Processors and Programmable Media Processors**

Digital signal processors are listed next in Table 5.1. The first DSP, the TI C67x [TI, 2003], is an 8-way VLIW operating at 225 MHz that targets floating-point applications, and has energy efficiency of 889 pJ per instruction. DSPs targeted for lower-precision fixed-point operation such as the TI C64x [Agarwala *et al.*, 2002], a 600 MHz 8-way VLIW, are able to provide improved energy efficiency over floating-point DSPs and microprocessors when normalized to the same technology, achieving 150 pJ per 16b operation. This improved efficiency is due to arithmetic units optimized for lower-precision fixed-point operation and with SIMD extensions in the C64x. In addition to C6x DSPs, there are a number of other VLIW DSPs and programmable media processors which achieve similar energy efficiencies such as the Analog TigerSharc [Olofsson and Lange, 2002], Trimedia [Rathnam and Slavenburg, 1996], the Starcore DSP [Brooks and Shearer, 2000], and others.

DSPs, programmable media processors, and special-purpose processors provide an energy efficiency advantage over microprocessors because they have kept pipeline lengths small and avoided speculative branch predictors for energy efficiency purposes. However, VLIW DSP architectures are not able to scale to tens of ALUs per processor, because they still rely on global register file and control structures in VLIW or superscalar microarchitectures. They also only exploit ILP and limited amounts of DLP through SIMD extensions, similar to microprocessors. As a result, they have area and energy efficiencies significantly better than general-purpose energy-inefficient microprocessors, but are still one to two orders of magnitude worse than special-purpose processors.

### 2.3.4 Vector Microprocessors

While SIMD extensions enable microprocessors and DSPs to exploit a small degree of DLP, vector processors [Russell, 1978] can exploit much more data parallelism directly with vector instructions and vector memory systems. As technology has advanced, vector processors on a single chip, or vector microprocessors have been become feasible [Wawrzynek *et al.*, 1996]. Recently, researchers have studied the use of vector microprocessors for media applications such as VIRAM [Kozyrakis, 2002] and others [Lee and Stoodley, 1998]. The performance and energy efficiency of VIRAM is shown in Table 5.1. It is able to provide

energy efficiencies competitive with DSPs at higher performance rates because of its ability to efficiently exploit DLP and its embedded memory system.

Vector processors directly exploit data parallelism by executing vector instructions such as vector adds or multiplies out of a vector register file. These vector instructions are similar to SIMD extensions in that they exploit inner-loop data parallelism in media applications, however, vector lengths are not constrained by the width of the vector units, allowing even more DLP to be exploited. Furthermore, vector memory systems are suitable for media processing because they are optimized for bandwidth and predictable strided accesses rather than conventional processors whose memory systems are optimized for reducing latency. For these reasons, vector processors are able to exploit significant data parallelism and compute intensity in media applications.

### 2.3.5 Chip Multiprocessors

Whereas vector microprocessors use SIMD execution to exploit DLP and achieve higher compute intensities, another approach to providing high arithmetic performance is chip multiprocessors (CMPs). In these solutions, multiple processor cores on the same chip each have their own thread of execution and mechanisms for on-chip communication and synchronization are provided. Some example research CMPs include RAW [Waingold *et al.*, 1997], Smart Memories [Mai *et al.*, 2000], and others. Other CMPs such as the Cradle 3SOC [Cradle, 2003] and Broadcom's Calisto (formerly Silicon Spice) [Nickolls *et al.*, 2002] have been proposed to specifically target lower-precision digital signal processing applications.

During media application execution, CMPs typically use thread-level parallelism to achieve high arithmetic performance by statically assigning tasks to some subset of the available on-chip cores. They can also use SIMD execution of multiple cores to exploit data parallelism within each task. Finally, CMPs are able to exploit producer-consumer locality by passing the output of one task directly to the input of another task without accessing global or off-chip memories. For all of these reasons, CMPs are able to provide arithmetic performance significantly higher than current DSPs or microprocessors by exploiting thread-level parallelism. As shown above, there are a wide variety of processors that can be used to run media applications. Special-purpose processors are inflexible, but are matched to both VLSI technology and media application characteristics. As a result, there is a large and growing gap between the performance efficiency of these fixed-function processors and programmable processors. The next section introduces stream processors as a way to bridge this efficiency gap.

## 2.4 Stream Processing

Stream processors are fully programmable processors that exploit the compute intensity, parallelism, and producer-consumer locality in media applications to provide performance efficiencies comparable to special-purpose processors [Rixner *et al.*, 1998; Khailany *et al.*, 2001; Rixner, 2001]. With stream processing, applications are expressed as *stream programs*, exposing the locality and parallelism inherent in media applications. A stream processor can then efficiently exploit the exposed locality with a bandwidth hierarchy of register files and can exploit the exposed parallelism with SIMD arithmetic clusters and multiple arithmetic units per cluster.

### 2.4.1 Stream Programming

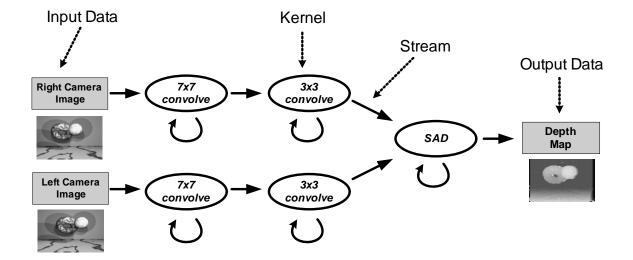

Media applications are naturally cast as stream programs. A stream program organizes data as *streams* and computation as a sequence of *kernels*. A stream is a finite sequence of related elements. Stream elements are records, such as 21-word triangles, or single-word RGBA pixels. A kernel reads from a set of input streams, performs the same computation on all elements of a stream, and writes a set of output streams. The stereo depth extractor when mapped into a stream program is shown in Figure 2.2. Arrows represent streams and circles represent kernels. In this application, each stream is a row of grayscale pixels. The convolution stage of the application is broken into two kernels: a 7x7 blurring filter followed by a 3x3 sharpen filter. The resulting streams are sent to the SAD kernel which computes the best disparity match in a row and outputs a row of pixels from a depth map.

Figure 1: Stereo Depth Extraction

Figure 2.2: Stereo depth extractor as a stream program

Stream programs expose the locality and parallelism in the algorithm to the compiler and hardware. Two key types of locality are exposed: kernel locality and producerconsumer locality. Kernel locality refers to intermediate data values that are live for only a short time during kernel execution, such as temporaries during a convolution filter computation. Producer-consumer locality refers to streams produced by one kernel and consumed by subsequent kernels. Finally, parallelism is exposed because a kernel typically executes the same kernel program on all elements of an input stream. By casting media applications as stream programs, hardware is able to take advantage of the abundant parallelism, compute intensity, and locality in media applications.

### 2.4.2 Stream Architecture

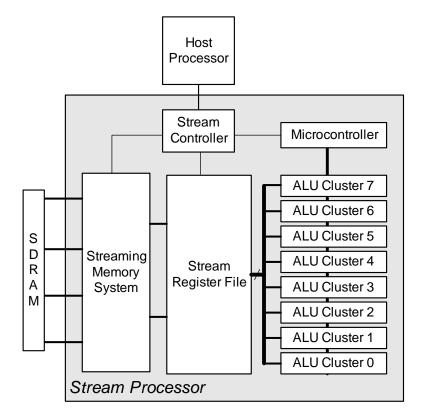

The Imagine stream processor architecture, which is optimized to take advantage of the application characteristics exposed by the stream programming model is shown graphically in Figure 2.3. A stream processor runs as a coprocessor to a host executing scalar code.

Figure 2.3: Stream Processor Block Diagram

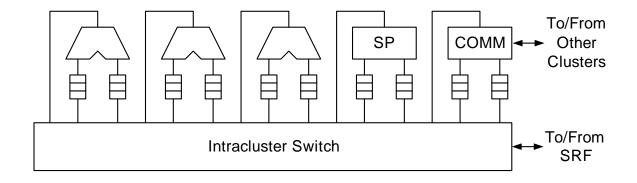

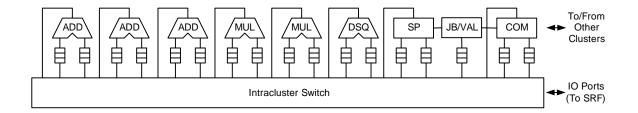

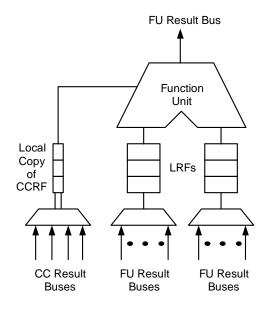

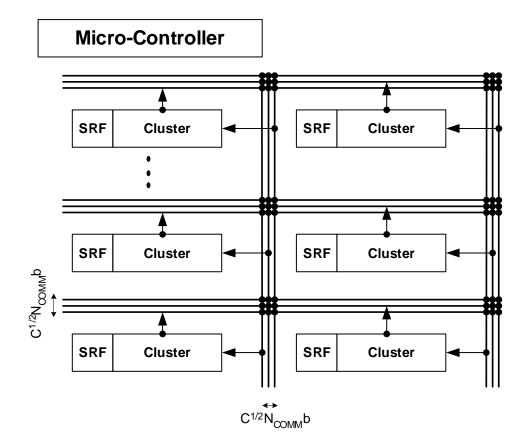

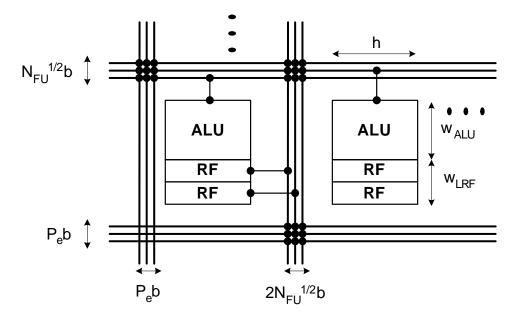

Instructions sent to the stream processor from the host are sequenced through a stream controller. The stream register file (SRF) is a large on-chip storage for streams. The microcontroller and ALU clusters execute kernels from a stream program. As shown in Figure 2.4, each cluster consists of ALUs fed by two local register files (LRFs) each, external ports for accessing the SRF, and an intracluster switch that connects the outputs of the ALUs and external ports to the inputs of the LRFs. In addition, there is a scratchpad (SP) unit, used for small indexed addressing operations within a cluster, and an intercluster communication (COMM) unit, used to exchange data between clusters. Imagine is a stream processor recently designed at Stanford University that contains six floating-point ALUs per cluster (three adders, two multipliers, and one divide-square-root unit) and eight clusters [Khailany *et al.*, 2001], and was fabricated in a CMOS technology with 0.18 micron metal spacing rules and 0.15 micron drawn gate length.

Figure 2.4: Arithmetic Cluster Block Diagram

Stream processors directly execute stream programs. Streams are loaded and stored from off-chip memory into the SRF. SIMD execution of kernels occurs in the arithmetic clusters. Although the stream processor in Figure 2.3 conatins eight arithmetic clusters, in general, the stream processor architecture can contain an arbitrary number of arithmetic clusters, represented by the variable C. For each iteration of a loop in a kernel, C clusters will read C elements in parallel from an input stream residing in the SRF, perform the exact same series of computations as specified by the kernel inner loop, and write C output elements in parallel back to an output stream in the SRF. Kernels repeat this for several loop iterations until all elements of the input stream have been read and operated on. Data-dependent conditionals in kernels are handled with conditional streams which, like predication, keep control flow in the kernel simple [Kapasi *et al.*, 2000]. However, conditional streams eliminate the extra computation required by predication by converting data-dependent control flow decisions into data-routing decisions.

Stream processors exploit parallelism and locality at both the kernel level and application level. During kernel execution, data-level parallelism is exploited with C clusters concurrently operating on C elements and instruction-level parallelism is exploited by VLIW execution within the clusters. At the application level, stream loads and stores can be overlapped with kernel execution, providing more concurrency. Kernel locality is exploited by stream processors because all temporary values produced and consumed during a kernel are stored in the cluster LRFs without accessing the SRF. At the application level, producer-consumer locality is exploited when streams are passed between subsequent kernels through the SRF, without going back to external memory.

The data in media applications that exhibits kernel locality and producer-consumer locality also has high data bandwidth requirements when compared to available off-chip memory bandwidth. Stream processors are able to support these large bandwidth requirements because their register files provide a three-tiered data bandwidth hierarchy. The first tier is the external memory system, optimized to take advantage of the predictable memory access patterns found in streams [Rixner et al., 2000a]. The available bandwidth in this stage of the hierarchy is limited by pin bandwidth and external DRAM bandwidth. Typically, during a stream program, external memory is only referenced for global data accesses such as input/output data. Programs are strip-mined so that the processor reads only one batch of the input dataset at a time. The second tier of the bandwidth hierarchy is the SRF, which is used to transfer streams between kernels in a stream program. Its bandwidth is limited by the available bandwidth of on-chip SRAMs. The third tier of the bandwidth hierarchy is the cluster LRFs and the intracluster switch between the LRFs which forwards intermediate data in a kernel between the ALUs in each cluster during kernel execution. The available bandwidth in this tier of the hierarchy is limited by the number of ALUs one can fit on a chip and the size of the intracluster switch between the ALUs.

The peak bandwidth rates of the three tiers of the data bandwidth hierarchy are matched to the bandwidth demands in typical media applications. For example, the Imagine processor contains 40 fully-pipelined ALUs and provides 2.3 GB/s of external memory bandwidth, 19.2 GB/s of SRF bandwidth, and 326.4 GB/s of LRF bandwidth. As discussed in Section 2.1, some media applications such as the stereo depth extractor require over 400 inherent ALU operations per memory reference. Imagine supports a ratio of ALU operations to memory words referenced of 28. Therefore, not only are stream processors in today's technology with tens of ALUs able to exploit this compute intensity, but as VLSI capacity continues to scale at 70% annually and as memory bandwidth continues to increase at 25% annually, this suggests that stream processors with thousands of ALUs could provide significant speedups on media applications without becoming memory bandwidth limited.

#### 2.4.3 Stream Processing Related Work

The stream processor architecture described above builds on previous work in data-parallel architectures and programming models.

Stream processors share with vector processors the ability to exploit large amounts of data paralellism and compute intensity, but they differ from vector processors in two key ways. First, vector processors execute simple vector instructions such as vector adds and multiplies on vectors located in the vector register file whereas stream processors execute microcode kernels in SIMD out of the stream register file. Second, the register files. These optimizations allow stream processors to both capture producer-consumer locality in the register file hierarchy and to provide improved scalability within the arithmetic clusters with the local register files. Related work in vector processors has explored the use of partitioned register files to improve their scalability [Kozyrakis and Patterson, 2003].

Although designing a programmable architecture to directly execute stream programs is new, programming models similar to the stream model have been proposed in previous work with fixed-function processors. One example of a fixed-function processor that directly executes the stream programming model is Cheops [Bove and Watlington, 1995]. It directly maps an application data-flow exposed by the stream programming model into hardware units and consists of a set of specialized stream processors where each processor accepts one or two data streams as input and produces one or two data streams as output. Data streams are either forwarded directly from one stream processor to the next according to the applications data-flow graph or transferred between memory and the stream processors.

Other researchers have proposed designing signal processing systems using signal flow graphs specified in Simulink [Simulink, 2002] or other programming models [Lee and Parks, 1995] that have many similarities with the stream programming model. With these systems, signal flow graphs can be synthesized to software running on DSPs [Bhattacharyya *et al.*, 1996; de Kock *et al.*, 2000] or can be mapped into fixed-function processors using hardware generators [Davis *et al.*, 2001]. Designing fixed-function processors with these techniques allows for high efficiency since available parallelism and producer-consumer

locality can easily be exploited. However, unlike programmable processors, fixed-function processors lack the flexibility to execute a wide variety of applications.

Recently, other researchers have applied these same techniques for exploiting parallelism and locality used in fixed-function processors to reconfigurable logic. Streams-C [Gokhale *et al.*, 2000] and others [Caspi *et al.*, 2001] have proposed mapping arithmetic kernels to blocks in FPGAs and mapping streams passed between kernels to FIFO-based communication channels between FPGA blocks. These techniques enable some degree of programmability with a high-level language and are able to exploit large amounts of parallelism in stream programs. However, this approach is inhibited by limitations in reconfigurable logic. When compared to fixed-function transistors, large area and energy overheads are incurred when a design is implemented in reconfigurable logic. Furthermore, since stream programs are being spatially mapped onto a fixed resource such as an FPGA, problems arise when applications are too complex to fit onto this fixed resource.

Finally, other researchers have also studied compiling and executing the stream programming model on chip multiprocessors. Streamit is a programming language that implements the stream model on the RAW CMP [Gordon *et al.*, 2002]. Like hardwired stream processors, CMPs executing compiled stream programs can exploit parallelism with threads and producer-consumer locality between processors to manage communication bandwidth effectively. Like CMPs, programmable stream processors also have the ability to exploit parallelism and locality. However, since CMPs are targeted to run a wide variety of applications and rely mostly on thread-level parallelism, they contain more general control and communication structures per processor. In contrast, stream processors are targeted specifically for media applications, and therefore can use data-parallel hardware to efficiently exploit the available parallelism and a register file organization to efficiently exploit the available locality.

### 2.4.4 VLSI Efficiency of Stream Processors

The bandwidth hierarchy provided by a stream architecture's register file organization allows stream processors to sustain a large percentage of peak performance with very modest off-chip memory bandwidth requirements. However, the other advantage of the register file organization is the area and energy efficiency derived from partitioning the register file storage into stream register files, arithmetic clusters, and local register files within the arithmetic clusters. This partitioning enables stream processors to scale to thousands of ALUs with significantly modest area and energy costs.

The area of a register file is the product of three terms: the number of registers R, the bits per register, and the size of a register cell. Asymptotically, with a large number of ports, each register cell has an area that grows with  $p^2$  because one wire is needed in the word-line direction, and another wire needed in the bit-line direction per register file port. Register file energy per access follows similar trends. Therefore, a highly multi-ported register file has area and power that grows asymptotically with  $Rp^2$  [Rixner *et al.*, 2000b]. A general-purpose processor containing N arithmetic units with a single centralized register file requires approximately 3N ports (two read ports for the operands and one wire port for the result per ALU). However, as N increases, working set sizes would also increase, meaning that R should also grow linearly with N. As a result, a single centralized multiported register file interconnecting N arithmetic units in a general-purpose microprocessor has area and power that grows with  $N^3$ , and would quickly begin to dominate processor area and power. As a result, partitioning register files is necessary in order to efficiently scale to large numbers of arithmetic units per processor.

Historically, register file partitioning has been used extensively in programmable processors in order to improve scalability, area and energy efficiency, and to reduce wire delay effects. For example, the TI C6x [Agarwala *et al.*, 2002] is a VLIW architecture split into two partitions, each containing a single multi-ported register file connected to four arithmetic units. Even in high-performance microprocessors not necessarily targeted for energy efficient operation, such as the Alpha 21264 [Gieseke *et al.*, 1997], register file partitioning has been used. In the stream architecture, register file partitioning occurs along three dimensions: distributed register files within the clusters, SIMD register files across the clusters, and the stream register organization between the clusters and memory. In the remainder of this section, we explain how the register file partition of Imagine along these three dimensions improves area and energy efficiency and is related to previous work on partitioned register files.

#### **Distributed Register Partitioning**